Verilog Part 2 Structural Verilog

Chapter 2 Verilog Syntax Structural Verilog And Timing Pdf Integer The document discusses modules in verilog, their structure, and components including ports, which enable communication between modules and their environment. it covers the definitions and types of ports, port declarations, and methods for connecting these ports to external signals. Structural verilog descriptions assemble several blocks of code and allow the introduction of hierarchy in a design. the following table lists the concepts of hardware structure and their descriptions.

6 Design Verilog Structural Instances Pdf This example uses the modules created in part 1 video and creates a larger circuit using structural verilog description. In this tutorial, i show how to design logic gates using structural modeling in verilog. structural modeling allows for the development and debugging of digital circuits more. In this chapter, we describe the verilog constructs to model signal assignments that are triggered by an event in order to accurately model sequential logic. we can then use these techniques to describe more complex sequential logic circuits, such as finite state machines and register transfer level systems. Structural modelling • at gate level, the circuit is described in terms of gates. (e.g., and, nand ) • hardware design at this level is intuitive for a user with a basic knowledge of digital logic design.

System Verilog Ii Pdf String Computer Science Computer Architecture In this chapter, we describe the verilog constructs to model signal assignments that are triggered by an event in order to accurately model sequential logic. we can then use these techniques to describe more complex sequential logic circuits, such as finite state machines and register transfer level systems. Structural modelling • at gate level, the circuit is described in terms of gates. (e.g., and, nand ) • hardware design at this level is intuitive for a user with a basic knowledge of digital logic design. After switch level modeling, structural modeling is the lowest level of abstraction in verilog. it is also called gate level modeling because we only describe a hardware in logic gates and their inteconnections. Identify the functions captured by the different operators available in verilog. understand how continuous assignment can be used to specify logic and wire arrangements. understand how module instancing is used to specify a netlist connecting modules together. Structural verilog allows for building modules from other modules to create a hierarchy. can instantiate our half adder module twice to reuse it in our full adder module to create a hierarchical design. This verilog documentation will focus on the structural level of description because it is efficient to code, yet offers a predictable mapping to hardware in the hands of a skilled user.

Verilog 6 Struct Modeling Ppt Pdf Read Only Memory Computer Data After switch level modeling, structural modeling is the lowest level of abstraction in verilog. it is also called gate level modeling because we only describe a hardware in logic gates and their inteconnections. Identify the functions captured by the different operators available in verilog. understand how continuous assignment can be used to specify logic and wire arrangements. understand how module instancing is used to specify a netlist connecting modules together. Structural verilog allows for building modules from other modules to create a hierarchy. can instantiate our half adder module twice to reuse it in our full adder module to create a hierarchical design. This verilog documentation will focus on the structural level of description because it is efficient to code, yet offers a predictable mapping to hardware in the hands of a skilled user.

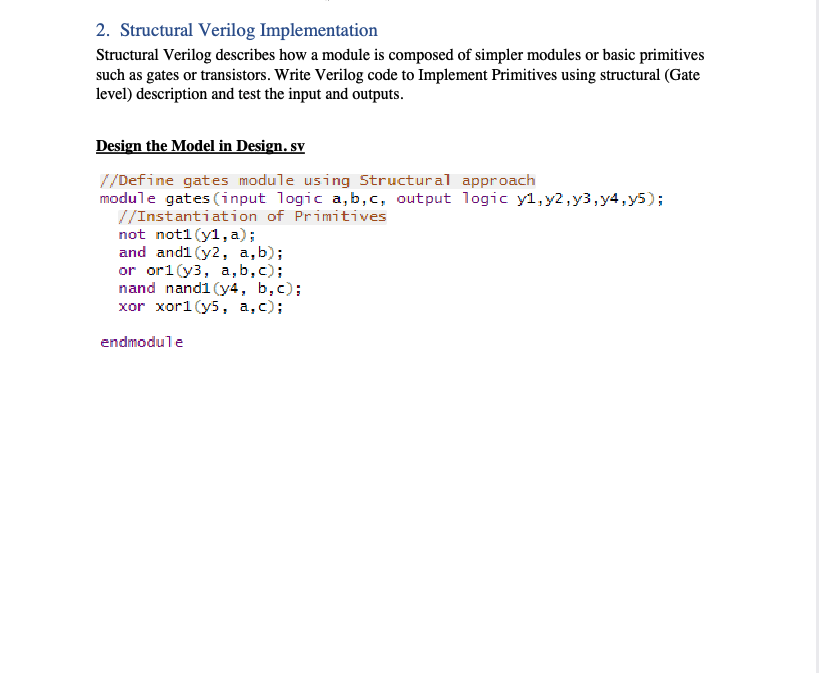

Solved 2 Structural Verilog Implementation Structural Chegg Structural verilog allows for building modules from other modules to create a hierarchy. can instantiate our half adder module twice to reuse it in our full adder module to create a hierarchical design. This verilog documentation will focus on the structural level of description because it is efficient to code, yet offers a predictable mapping to hardware in the hands of a skilled user.

Comments are closed.