Verilog Tutorial Part Ii Structural Descriptions Structural Descriptions

Verilog Tutorial Part Ii Structural Descriptions Structural Descriptions Structural verilog descriptions assemble several blocks of code and allow the introduction of hierarchy in a design. the following table lists the concepts of hardware structure and their descriptions. A structural description in verilog a is any description in which a module instantiates another module within the scope of its definition. a structural definition for the sys tem will define an explicit hierarchy in the design.

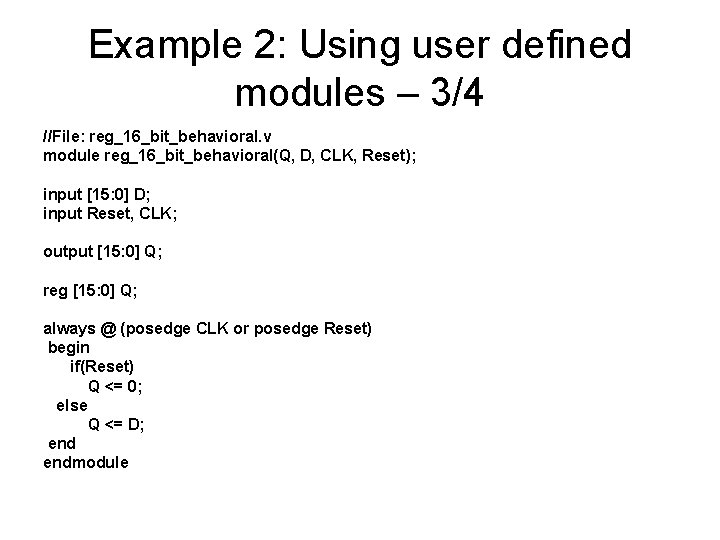

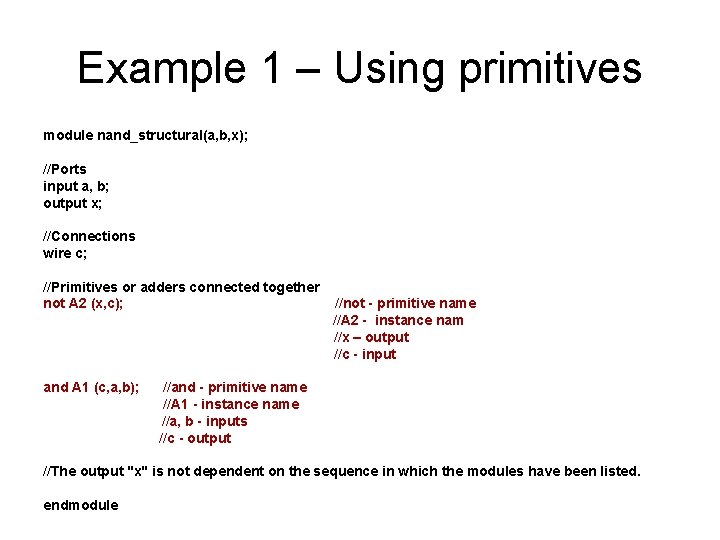

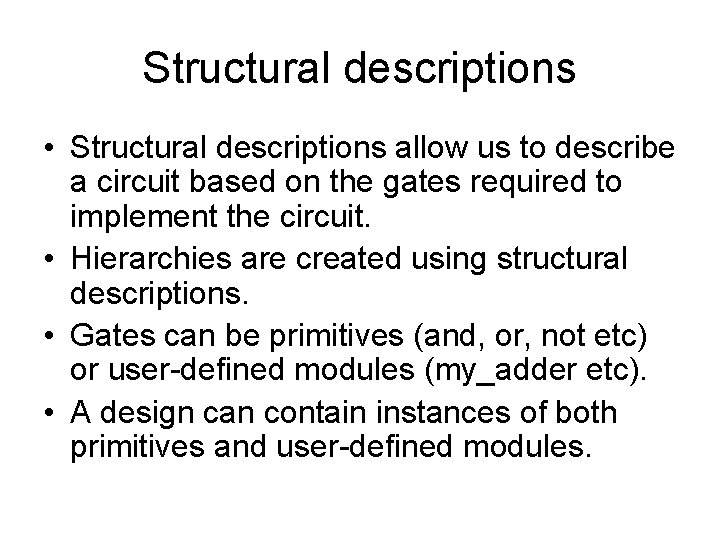

Verilog Tutorial Part Ii Structural Descriptions Structural Descriptions Structural descriptions • structural descriptions allow us to describe a circuit based on the gates required to implement the circuit. • hierarchies are created using structural descriptions. • gates can be primitives (and, or, not etc) or user defined modules (my adder etc). Structural description in verilog is utilized when the hardware components of a system, such as and, or, and not gates, are known, making it suitable for specific design constraints. This verilog documentation will focus on the structural level of description because it is efficient to code, yet offers a predictable mapping to hardware in the hands of a skilled user. Learn structural design with verilog. covers modeling, operators, flip flops, state machines, and style guidelines. ideal for college level electrical engineering.

Verilog Tutorial Part Ii Structural Descriptions Structural Descriptions This verilog documentation will focus on the structural level of description because it is efficient to code, yet offers a predictable mapping to hardware in the hands of a skilled user. Learn structural design with verilog. covers modeling, operators, flip flops, state machines, and style guidelines. ideal for college level electrical engineering. Verilog structural description defines a connection of components that form a physical circuit. this chapter details the construction of structural descriptions, in the following major sections:. The definition of behavioral description is one where architecture (vhdl) or module (verilog) includes the predefined word process (vhdl) or always or initial (verilog). In this exercise you will create the structural systemverilog description of four logic functions. note that you must use structural systemverilog rather than dataflow systemverilog to complete this assignment. In this description, details of the logic diagram of the system are not needed; what is needed is how the output behaves in response to a change in the input.

Comments are closed.