Verilog Part 2 Modelling Styles

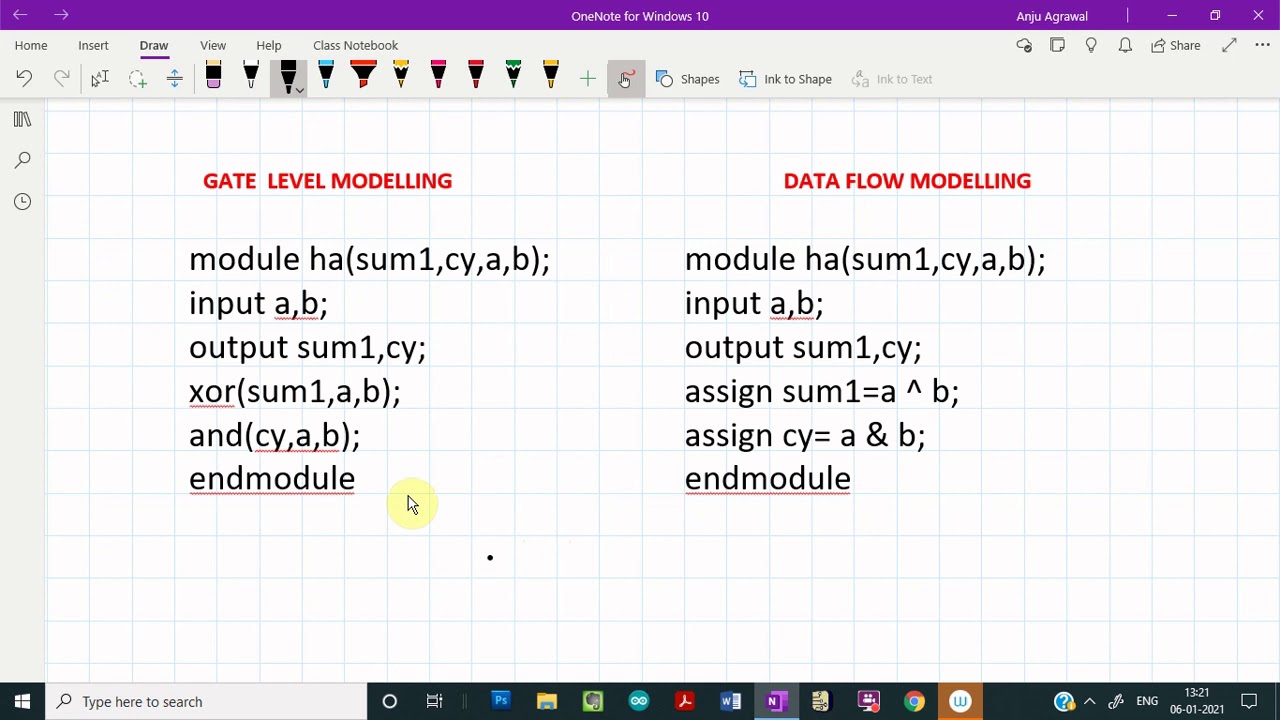

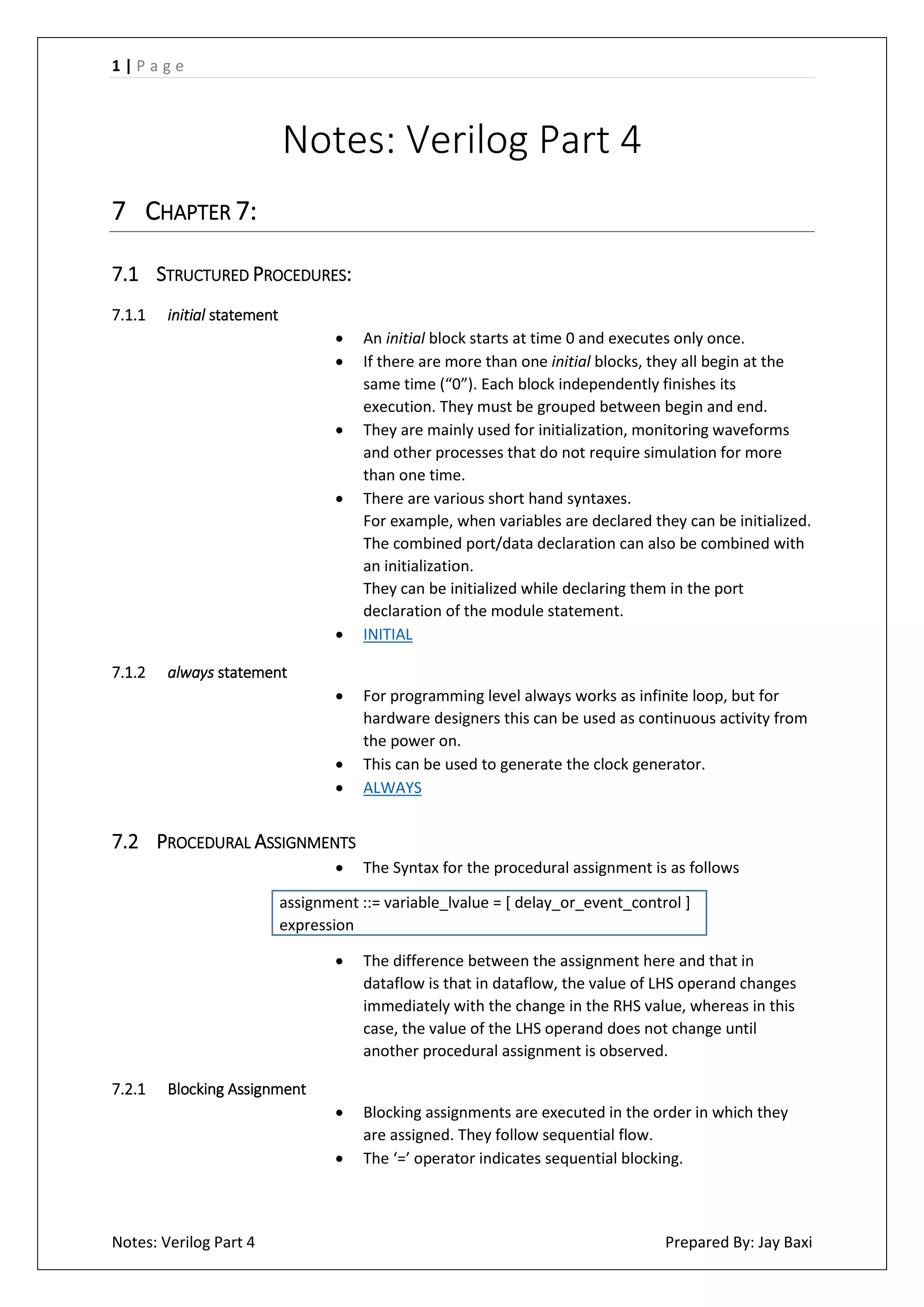

Introduction To Verilog Modelling Styles Pdf Parameter Computer Verilog provides several types of modeling techniques, each suited for different purposes. in this tutorial, we’ll explore the three primary types of verilog modeling: behavioral modeling, dataflow modeling, and structural modeling. It specifies how a module is composed of smaller sub modules and or primitive logic gates, and how these components are interconnected. it is analogous to a netlist or a schematic diagram.

Verilog Hdl Exploring Different Modelling Styles In this comprehensive guide, we will explore the different techniques used in verilog modelling, providing valuable insights to aid you in your circuit design endeavors. Verilog language has the capability of designing a module in several coding styles. depending on the needs of a design, internals of each module can be defined at four level of abstractions. The document discusses different modeling techniques in verilog hdl, including behavioral, dataflow, and gate level modeling. it describes four levels of abstraction behavioral, dataflow, gate level, and switch level modeling. The course will introduce the participants to the verilog hardware description language. it will help them to learn various digital circuit modeling issues using verilog, writing test benches, and some case studies.

Types Of Modelling In Verilog Infoupdate Org The document discusses different modeling techniques in verilog hdl, including behavioral, dataflow, and gate level modeling. it describes four levels of abstraction behavioral, dataflow, gate level, and switch level modeling. The course will introduce the participants to the verilog hardware description language. it will help them to learn various digital circuit modeling issues using verilog, writing test benches, and some case studies. The document outlines three main verilog design styles: dataflow, behavioral, and structural modeling. dataflow is used for known boolean expressions, behavioral modeling employs 'always' blocks for sequential logic, and structural modeling involves instantiating blocks of code. Verilog has three types of case statements: case, casex, and casez performs bitwise match of expression and case item both must have same bitwidth to match!. Each modeling style offers a different perspective, from high level behavior to transistor detail. Verilog language has the capability of designing a module in several coding styles. depending on the needs of a design, internals of each module can be defined at four level of abstractions.

Types Of Modelling In Verilog The document outlines three main verilog design styles: dataflow, behavioral, and structural modeling. dataflow is used for known boolean expressions, behavioral modeling employs 'always' blocks for sequential logic, and structural modeling involves instantiating blocks of code. Verilog has three types of case statements: case, casex, and casez performs bitwise match of expression and case item both must have same bitwidth to match!. Each modeling style offers a different perspective, from high level behavior to transistor detail. Verilog language has the capability of designing a module in several coding styles. depending on the needs of a design, internals of each module can be defined at four level of abstractions.

Types Of Modelling In Verilog Each modeling style offers a different perspective, from high level behavior to transistor detail. Verilog language has the capability of designing a module in several coding styles. depending on the needs of a design, internals of each module can be defined at four level of abstractions.

Notes Verilog Part 4 Behavioural Modelling Pdf

Comments are closed.