Verilog Lab 8 Pdf Electronics Computer Science

Verilog Lab 8 Pdf Electronics Computer Science The document outlines a lab experiment focused on the implementation, simulation, and synthesis of sequential circuits using verilog hdl, specifically d flip flops, registers, and counters. Contribute to thenageek altera university program lab solutions development by creating an account on github.

Verilog Lab Pdf Fsm is a very useful tool for designing sequential logic. a fsm is composed from a collection of flip flops. this collection is often referred to as a register. state is represented by a unique value stored in this register. View assignment dsd lab 8 23 cp (1).pdf from electrica electronic at continental university of sciences and engineering. digital system design lab # 08 spring 2026 computer engineering. Experiment 11 counter up down (bcd and binary) , sequential counters using verilog behavioral description. This section provides the lecture notes from the course.

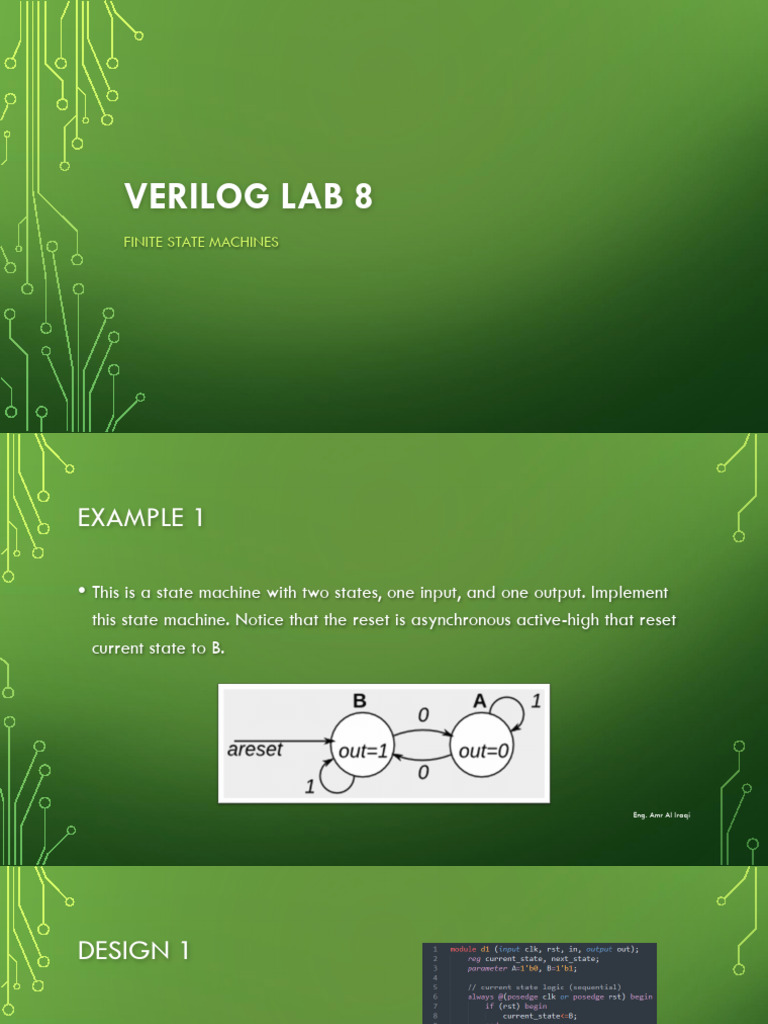

Verilog Hdl Lab Circuit Design Techniques Pdf Hardware Description Experiment 11 counter up down (bcd and binary) , sequential counters using verilog behavioral description. This section provides the lecture notes from the course. Cecs 201 lab 8 "finite state machine fsm" lab report: lab assignment 8 "finite state machine fsm" goal: the purpose of this lab is to better our understanding of the design, implementation, and function of fsms, as well as learn how to model fsm in verilog. Problem analysis: identify, formulate, review research literature, and analyze complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences. Loading…. To simplify the given boolean expressions and realize using verilog program.

Verilog Programming With Fpga Kit Pdf Logic Gate Field Cecs 201 lab 8 "finite state machine fsm" lab report: lab assignment 8 "finite state machine fsm" goal: the purpose of this lab is to better our understanding of the design, implementation, and function of fsms, as well as learn how to model fsm in verilog. Problem analysis: identify, formulate, review research literature, and analyze complex engineering problems reaching substantiated conclusions using first principles of mathematics, natural sciences, and engineering sciences. Loading…. To simplify the given boolean expressions and realize using verilog program.

Lab 8 Half And Full Adder Verilog Modelling Pdf Computing Digital Loading…. To simplify the given boolean expressions and realize using verilog program.

04 Verilog Codes For Basic Components 2021f Pdf Digital

Comments are closed.