Lab 8 Data Flow Verilog

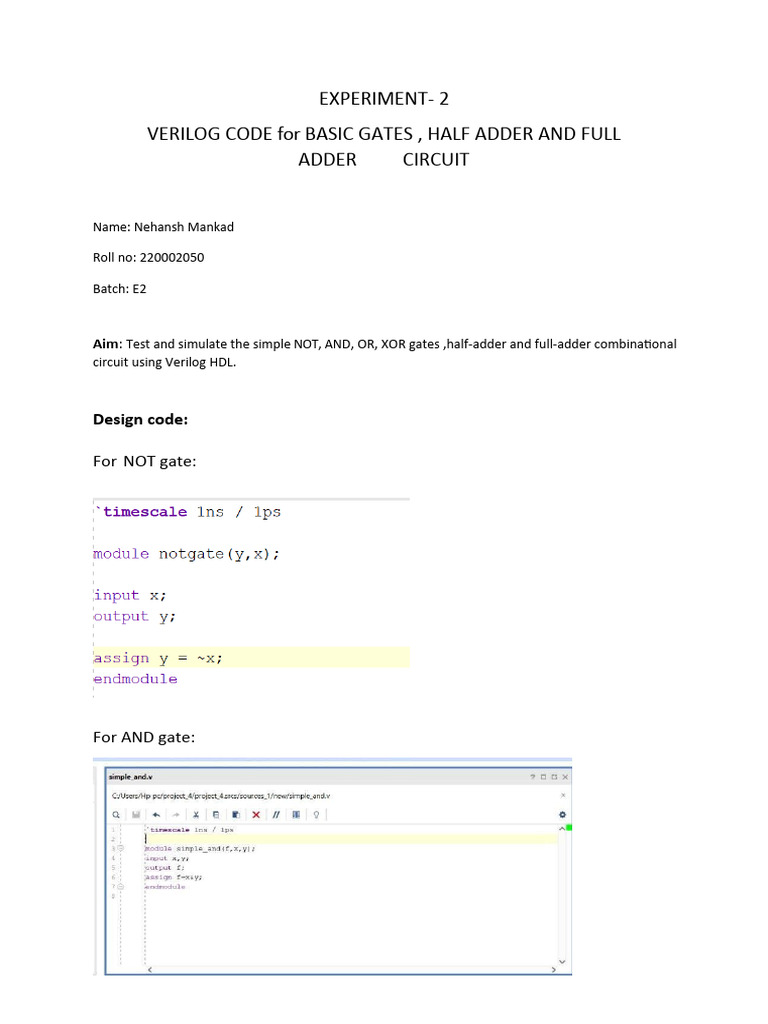

Lab 6 Verilog Data Flow Pdf Theory Of Computation Computer Vlsi lab report 8 free download as pdf file (.pdf), text file (.txt) or read online for free. this lab report describes implementing various digital logic circuits using verilog and data flow modeling. In this introduction, we’ll explore the basics of data flow modeling, how it enhances the readability and flexibility of your code, and why it’s a fundamental approach for efficient hardware description.

Data Flow Modeling In Verilog Pdf Hardware Description Language An alu was implemented to add, subtract, increment, decrement, and, or, and not through the implementation of verilog and a basys3 board. Learn how data flow modeling works in verilog, how to use the assign statement and operators, and its role in designing combinational logic efficiently. 西安交通大学本科生课程 数字逻辑与数字系统实验. contribute to lllvcs digital logic experiment development by creating an account on github. Lab task 02: write verilog code for 4 2 and 8 3 encoder using gates gate level modeling.

Verilog Lab 1 Pdf 西安交通大学本科生课程 数字逻辑与数字系统实验. contribute to lllvcs digital logic experiment development by creating an account on github. Lab task 02: write verilog code for 4 2 and 8 3 encoder using gates gate level modeling. Designing circuits using dataflow modeling in verilog involves a systematic approach to create efficient and reliable digital designs. in this section, we will explore the key steps involved in the process and provide practical examples to illustrate the concept. Data flow modeling in verilog is a middle ground abstraction: it allows you to describe how data is combined and flows through nets using continuous assignments, with optional delays, without detailing the internal gates. In this lab you will learn how to model a combinatorial circuit using data flow modeling style of verilog hdl. you will understand how to use verilog logical operators in data flow modeling style constructs. you will use ise simulator to simulate the design. Dataflow modeling is the second abstraction level in verilog hdl. this post explains the concept, the syntax, rules and the steps to use dataflow modeling.

Verilog Lab 258 220002076 Pdf Electrical Circuits Electronics Designing circuits using dataflow modeling in verilog involves a systematic approach to create efficient and reliable digital designs. in this section, we will explore the key steps involved in the process and provide practical examples to illustrate the concept. Data flow modeling in verilog is a middle ground abstraction: it allows you to describe how data is combined and flows through nets using continuous assignments, with optional delays, without detailing the internal gates. In this lab you will learn how to model a combinatorial circuit using data flow modeling style of verilog hdl. you will understand how to use verilog logical operators in data flow modeling style constructs. you will use ise simulator to simulate the design. Dataflow modeling is the second abstraction level in verilog hdl. this post explains the concept, the syntax, rules and the steps to use dataflow modeling.

Verilog Dataflow Modeling Pdf In this lab you will learn how to model a combinatorial circuit using data flow modeling style of verilog hdl. you will understand how to use verilog logical operators in data flow modeling style constructs. you will use ise simulator to simulate the design. Dataflow modeling is the second abstraction level in verilog hdl. this post explains the concept, the syntax, rules and the steps to use dataflow modeling.

Lab 6 Verilog Data Flow Pdf Bit Digital Electronics

Comments are closed.