Verilog Lab Pdf

Verilog Lab 4 Pdf Electricity Electrical Circuits Simulating and studying the static and dynamic electrical behavior of digital circuits in verilog involves understanding and analyzing how the circuit behaves under different conditions, focusing on both its steady state (static) and transient (dynamic) characteristics. Design of 8 to 1 multiplexer demultiplexer aim: to design 8x1 multiplexer demultiplexer using verilog and simulate the design.

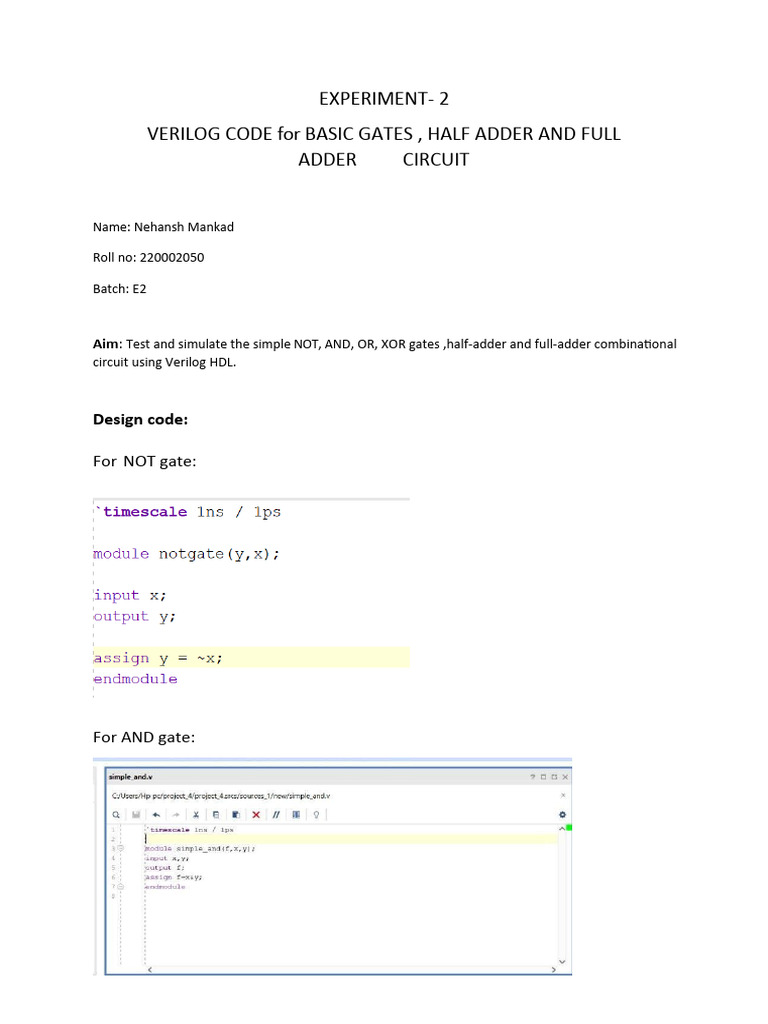

Verilog Lab 258 220002076 Pdf Electrical Circuits Electronics Verilog is one of the hdl languages available in the industry for designing the hardware. verilog allows us to design a digital design at behavior level, register transfer level (rtl), gate level and at switch level. This manual introduces the basic and most common verilog behavioral and gate level modelling constructs, as well as verilog compiler directives and system functions. Lab 10 digital design using hdl(verilog) the goal of this lab is to get familiar with digital modeling in verilog hardware description language (hdl) and to learn how to handle the simulator. the goal is also to interpret outputs from a simulator and to understand how ve. g code is interpreted by the simulator. for t. Since we expect you to write your verilog ahead of time, and verilog is nothing more than a bunch of standard text in a file with a *.v extension, you can do this part of the lab entirely from home in your favorite text editor (we recommend notepad).

Lab Exercises Digital Logic Verilog Lab10 Design Files De1 Soc Part3 Write a verilog program to implement the same half adder circuit using data ow modeling and simulate your circuit again. note: you don't have to specify your waveforms as you have already saved them in a le. Verilog laboratory manual free download as pdf file (.pdf), text file (.txt) or read online for free. this document contains a laboratory manual prepared by g.v.k. sharma of the department of electronics and communication engineering at gitam institute of technology. In lab, we will be using a hardware description language (hdl) called verilog. writing in verilog lets us focus on the high‐level behavior of the hardware we are trying to describe rather than the low‐level behavior of every single logic gate. The lab tries to show through simulation the difference between ffs with asynchronous and synchronous reset and also with or without a data‐enable.

Verilog Lab Manual Sapna Electronics Diploma And Engineering In lab, we will be using a hardware description language (hdl) called verilog. writing in verilog lets us focus on the high‐level behavior of the hardware we are trying to describe rather than the low‐level behavior of every single logic gate. The lab tries to show through simulation the difference between ffs with asynchronous and synchronous reset and also with or without a data‐enable.

Comments are closed.