Understanding Memory Consistency Models In Parallel Computing Course Hero

Understanding Memory Consistency Models In Parallel Computing Course Hero We are especially interested in the influence that weakened consistency models have on language, compiler, and runtime system design. we conclude that tighter interaction between those parts and the memory system might improve performance considerably. Memory consistency models define rules for shared memory access in parallel systems. they ensure predictable behavior across processors and threads, crucial for writing correct parallel code.

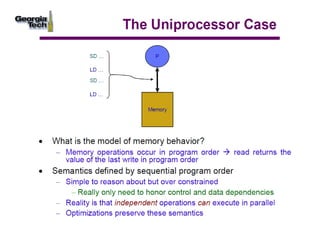

Solution Memory Consistency Models Studypool Lecture 14 slide 3eecs 570 memory consistency model a memory (consistency) model specifies the order in which memory accesses performed by one thread become visible to other threads in the program. Consistency models consistency models are not about memory operations from different processors. consistency models are not about dependent memory operations in a single processor’s instruction stream (these are respected even by processors that reorder instructions). Memory consistency order in which memory operations appear to occur across threads • memory consistency defines the rules that determine when memory operations (reads and writes) from one thread become visible to other threads in a parallel program. Sequential consistency (sc) • lamport (1979) definition: • the result of any execution is the same as if the operations of all the processors were executed in some sequential order, and the operations of each individual processor appear in this sequence in the order specified by its program.

Memory Consistency Models Pdf Memory consistency order in which memory operations appear to occur across threads • memory consistency defines the rules that determine when memory operations (reads and writes) from one thread become visible to other threads in a parallel program. Sequential consistency (sc) • lamport (1979) definition: • the result of any execution is the same as if the operations of all the processors were executed in some sequential order, and the operations of each individual processor appear in this sequence in the order specified by its program. High performance processors take advantage of disjoint operations that can be performed in parallel through instruction level parallelism (ilp). A multiprocessor normally advertises the supported memory consistency model this essentially tells the programmer what the possible correct outcome(s) of a program could be when run on that machine. View f91217d4 c757 400e 90e3 272add528593 chapter 5 part 1 parallel architectures.pdf from compsci 1027a at western university. chapter 5 part 1: parallel architectures created class @march 24, 2025. Weaker memory models & memory fence instructions • architectures with weaker memory models provide memory fence instructions to prevent otherwise permitted reorderings of loads and stores.

Memory Consistency Models And Basics Pdf High performance processors take advantage of disjoint operations that can be performed in parallel through instruction level parallelism (ilp). A multiprocessor normally advertises the supported memory consistency model this essentially tells the programmer what the possible correct outcome(s) of a program could be when run on that machine. View f91217d4 c757 400e 90e3 272add528593 chapter 5 part 1 parallel architectures.pdf from compsci 1027a at western university. chapter 5 part 1: parallel architectures created class @march 24, 2025. Weaker memory models & memory fence instructions • architectures with weaker memory models provide memory fence instructions to prevent otherwise permitted reorderings of loads and stores.

Comments are closed.