Memory Consistency Models And Basics Pdf

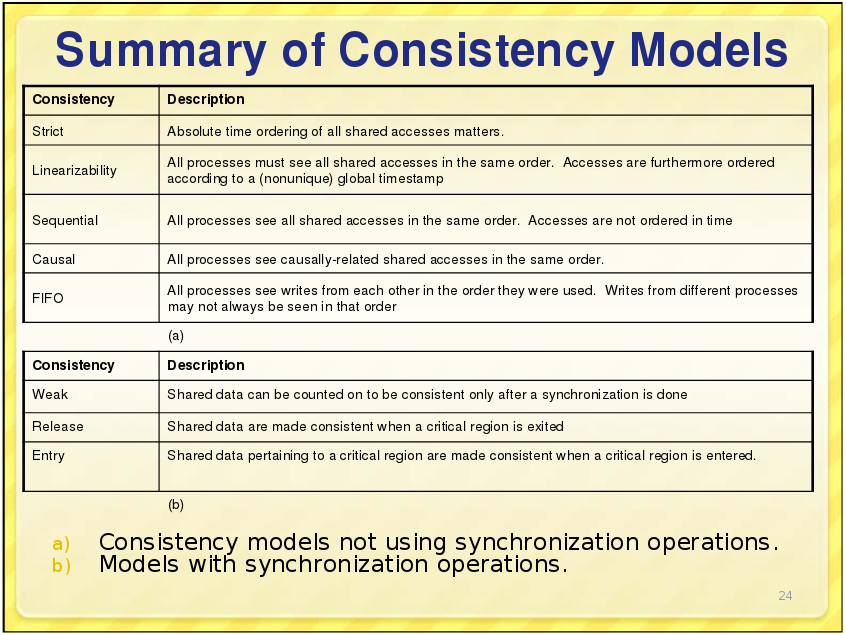

L43 Models Of Memory Consistency Pdf Cpu Cache Parallel Computing Weaker memory models & memory fence instructions • architectures with weaker memory models provide memory fence instructions to prevent otherwise permitted reorderings of loads and stores. Consistency models are not about dependent memory operations in a single processor’s instruction stream (these are respected even by processors that reorder instructions).

Memory Consistency Model Pdf Computing Computer Data Abstract: the memory consistency model for a shared memory multiprocessor specifies the behaviour of memory with respect to read and write operations from multiple processors. Many processors today relax the consistency model to get rid of complex hardware and achieve some extra performance at the cost of making program reasoning complex. “a multiprocessor is sequentially consistent if the result of any execution is the same as if the operations of all the processors were executed in some sequential order, and the operations of each individual processor appear in this sequence in the order specified by its program.”. Memory models, which describe the semantics of shared variables, are crucial to both correct multithreaded applications and the entire underlying implementation stack.

Memory Consistency Models Kavya G “a multiprocessor is sequentially consistent if the result of any execution is the same as if the operations of all the processors were executed in some sequential order, and the operations of each individual processor appear in this sequence in the order specified by its program.”. Memory models, which describe the semantics of shared variables, are crucial to both correct multithreaded applications and the entire underlying implementation stack. Relaxed memory consistency issues arise from the optimization of reordering memory operations. (consistency is unrelated to whether or not caches exist in the system.). This document discusses several hardware memory models including total store order (tso), processor consistency (pc), and weak ordering. tso allows loads to bypass earlier stores to different addresses but maintains order of loads and stores. Sequential consistency is not really about dependent memory operations in a single processor’s instruction stream (these are respected even by processors that reorder instructions). Uk abstract. memory consistency models (mcms) are at the heart of con c. rrent programming. they represent the behaviour of concurrent pro grams at the chip level. to test these models small program snippets cal.

Memory Consistency Models And Basics Pdf Relaxed memory consistency issues arise from the optimization of reordering memory operations. (consistency is unrelated to whether or not caches exist in the system.). This document discusses several hardware memory models including total store order (tso), processor consistency (pc), and weak ordering. tso allows loads to bypass earlier stores to different addresses but maintains order of loads and stores. Sequential consistency is not really about dependent memory operations in a single processor’s instruction stream (these are respected even by processors that reorder instructions). Uk abstract. memory consistency models (mcms) are at the heart of con c. rrent programming. they represent the behaviour of concurrent pro grams at the chip level. to test these models small program snippets cal.

Comments are closed.