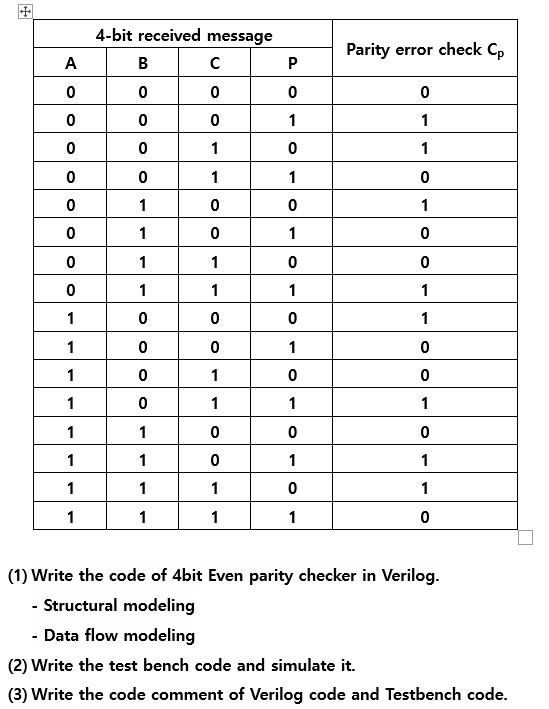

Solved Verilog Question 4 Bit Received Message Parity Error Check Cp

Solved Verilog Question 4 Bit Received Message Parity Error Check Cp It uses xor gates to calculate the parity bit. the input is a 4 bit data in and the output is the parity bit cp. testbench code comments this testbench code tests the functionality of the 4 bit even parity checker. Parity checker: checks the received data along with the parity bit to detect single bit errors. this project demonstrates concepts of error detection and combinational logic in digital systems.

Solved 4 Implement A 4 Bit Even Parity Checker At The Chegg Using this code to implement a 4 bit even parity checker, we can take data in as input, calculate an even parity bit through an xor operation, and perform an xor operation with parity bit to detect errors. 1 i'm trying to write a code to check for even odd parity in verilog. here's the testbench code: however, i'm only getting one as output for the variable answer, no matter what. there seems to be some problem in the logical part. what could be it?. This project explores the design and implementation of a parity generator and checker system using verilog hdl. it focuses on error detection in digital communication by generating parity bits and verifying data integrity during transmission, ensuring reliable data transfer in various applications. If the recalculated parity matches the received parity, the data is valid, and the error flag is set to 0. the error flag is the key indicator in this system.

Github Shashi18 Parity Bit Checker Verilog Parity Bit Checker This project explores the design and implementation of a parity generator and checker system using verilog hdl. it focuses on error detection in digital communication by generating parity bits and verifying data integrity during transmission, ensuring reliable data transfer in various applications. If the recalculated parity matches the received parity, the data is valid, and the error flag is set to 0. the error flag is the key indicator in this system. This page contains verilog tutorial, verilog syntax, verilog quick reference, pli, modeling memory and fsm, writing testbenches in verilog, lot of verilog examples and verilog in one day tutorial. Data word bits, along with parity bits, are called a codeword. the parity bit is added to the message bits on the sender side to help in error detection at the receiver side. This verilog program implements a system for transmitting data with error detection and potential correction using crc (cyclic redundancy check) and parity check methods. A parity odd checker is a digital circuit that takes a set of data bits along with a parity bit as input and checks whether the combination of data bits and the provided parity bit results in odd parity or not.

Comments are closed.