Verilog Tutorial For Beginners 9 Odd Parity Program Using Assign Statement

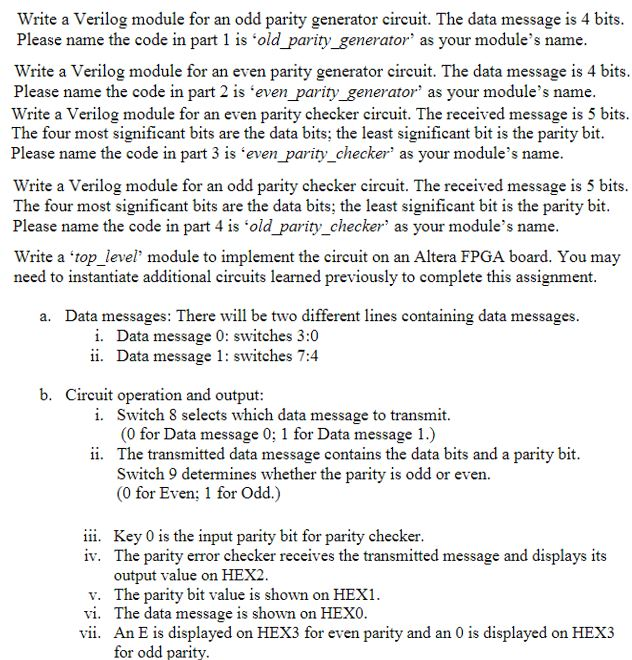

Using Verilog Hdl I Have The Modules For Odd Parity Chegg Verilog tutorial for beginners 9 odd parity program using assign statement jamia hamdard 99 subscribers subscribe. This page contains verilog tutorial, verilog syntax, verilog quick reference, pli, modeling memory and fsm, writing testbenches in verilog, lot of verilog examples and verilog in one day tutorial.

Verilog Assign Statement Explore the verilog assign statement, its applications in combinational logic and more; with practical examples ranging from and gates to complex modules. Learn the basics of the verilog assign statement with clear syntax, practical examples, and common mistakes to avoid. understand how continuous assignment works, the difference between wire and reg, and how to design combinational circuits effectively. The module shown below takes two inputs and uses an assign statement to drive the output z using part select and multiple bit concatenations. treat each case as the only code in the module, else many assign statements on the same signal will definitely make the output become x. Compiled set of verilog codes for beginners. can help you with getting started with basics of verilog. basic verilog codes odd parity generator.v at main · bharadwaj r basic verilog codes.

Verilog Assign Statement The module shown below takes two inputs and uses an assign statement to drive the output z using part select and multiple bit concatenations. treat each case as the only code in the module, else many assign statements on the same signal will definitely make the output become x. Compiled set of verilog codes for beginners. can help you with getting started with basics of verilog. basic verilog codes odd parity generator.v at main · bharadwaj r basic verilog codes. Using this code to implement a 4 bit odd parity generator, you can take data in as input, perform an xor operation to generate a parity bit, and output it as parity bit. Learn how to use verilog assign statement for continuous assignments, combinational logic, and hardware design. I will explain combinational logic in verilog, followed by 5 detailed examples, including rtl (register transfer level) code and test benches. in combinational logic circuits, the output is determined by the present state of the inputs. Dataflow modeling is one of the three fundamental modeling styles in verilog, alongside gate level and behavioral modeling. it describes hardware at the register transfer level (rtl) using continuous assignment statements.

Verilog Assign Statement Using this code to implement a 4 bit odd parity generator, you can take data in as input, perform an xor operation to generate a parity bit, and output it as parity bit. Learn how to use verilog assign statement for continuous assignments, combinational logic, and hardware design. I will explain combinational logic in verilog, followed by 5 detailed examples, including rtl (register transfer level) code and test benches. in combinational logic circuits, the output is determined by the present state of the inputs. Dataflow modeling is one of the three fundamental modeling styles in verilog, alongside gate level and behavioral modeling. it describes hardware at the register transfer level (rtl) using continuous assignment statements.

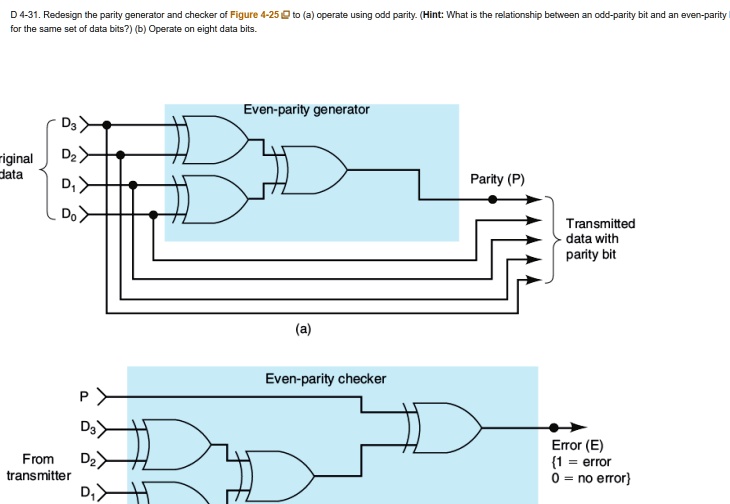

Solved D 4 31 Redesign The Parity Generator And Checker Of Figure 4 I will explain combinational logic in verilog, followed by 5 detailed examples, including rtl (register transfer level) code and test benches. in combinational logic circuits, the output is determined by the present state of the inputs. Dataflow modeling is one of the three fundamental modeling styles in verilog, alongside gate level and behavioral modeling. it describes hardware at the register transfer level (rtl) using continuous assignment statements.

Solved Write Vhdl Code For 9 Bit Odd Or Even Parity Checker Chegg

Comments are closed.