Parity Verilog Tutorial

Github Harshit 0017 Verilog Parity Generator A Synthesizable Serial Learn step by step to write a verilog program for 8 bit parity generator and checker circuits with output verification. This page contains verilog tutorial, verilog syntax, verilog quick reference, pli, modeling memory and fsm, writing testbenches in verilog, lot of verilog examples and verilog in one day tutorial.

Verilog Tutorial Parity generation in verilog: given below are 5 parity generation circuits. circuit 1: circuit 2, 4: circuit 3, 5: simple combinational parity generator. parity pc is registered latched and given to the output port. input x[7:0] is registered as xr[7:0] or latched as xl[7:0] before producing parity. 1 i'm trying to write a code to check for even odd parity in verilog. here's the testbench code: however, i'm only getting one as output for the variable answer, no matter what. there seems to be some problem in the logical part. what could be it?. A parity generator is a digital circuit that takes a set of data bits as input and generates a single parity bit as output. the purpose of the parity bit is to provide basic error detection in data transmission or storage systems. Using this code to implement a 4 bit odd parity generator, you can take data in as input, perform an xor operation to generate a parity bit, and output it as parity bit.

Verilog Tutorial A parity generator is a digital circuit that takes a set of data bits as input and generates a single parity bit as output. the purpose of the parity bit is to provide basic error detection in data transmission or storage systems. Using this code to implement a 4 bit odd parity generator, you can take data in as input, perform an xor operation to generate a parity bit, and output it as parity bit. This page provides a verilog code implementation for a 2d parity check generator. the code segments and arranges incoming 32 bit data into a 4x8 array, calculates row wise and column wise parity, and outputs a 45 bit parity vector. The document describes designing a parity checker using verilog. it contains the aim, apparatus required, block diagram, theory of parity checking, verilog code for the parity checker module and testbench module, and a sample testbench waveform. Enjoy the videos and music you love, upload original content, and share it all with friends, family, and the world on . In the case of even parity, the number of bits whose value is 1 in a given set are counted. if that total is odd, the parity bit value is set to 1, making the total count of 1's in the set an even number. if the count of ones in a given set of bits is already even, the parity bit's value remains 0. in the case of odd parity, the situation is.

Verilog Code For Parity Encoder This page provides a verilog code implementation for a 2d parity check generator. the code segments and arranges incoming 32 bit data into a 4x8 array, calculates row wise and column wise parity, and outputs a 45 bit parity vector. The document describes designing a parity checker using verilog. it contains the aim, apparatus required, block diagram, theory of parity checking, verilog code for the parity checker module and testbench module, and a sample testbench waveform. Enjoy the videos and music you love, upload original content, and share it all with friends, family, and the world on . In the case of even parity, the number of bits whose value is 1 in a given set are counted. if that total is odd, the parity bit value is set to 1, making the total count of 1's in the set an even number. if the count of ones in a given set of bits is already even, the parity bit's value remains 0. in the case of odd parity, the situation is.

Verilog Code For Parity Encoder Enjoy the videos and music you love, upload original content, and share it all with friends, family, and the world on . In the case of even parity, the number of bits whose value is 1 in a given set are counted. if that total is odd, the parity bit value is set to 1, making the total count of 1's in the set an even number. if the count of ones in a given set of bits is already even, the parity bit's value remains 0. in the case of odd parity, the situation is.

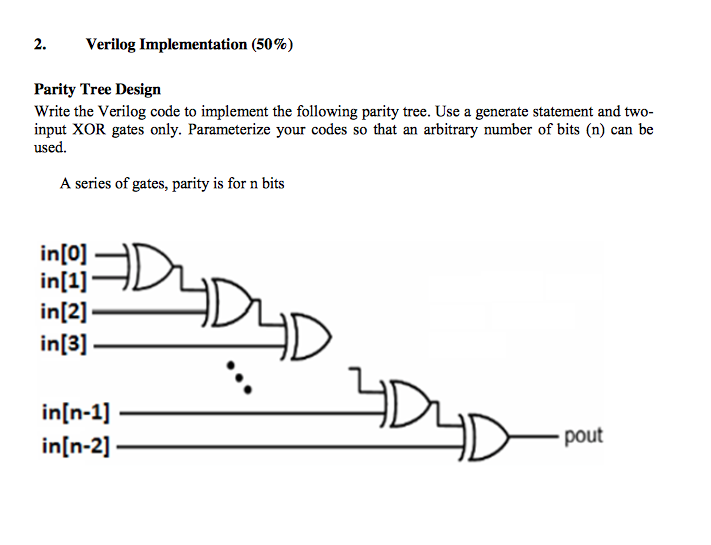

Solved Verilog Implementation 50 Parity Tree Design Chegg

Comments are closed.