Verilog Code For Parity Encoder

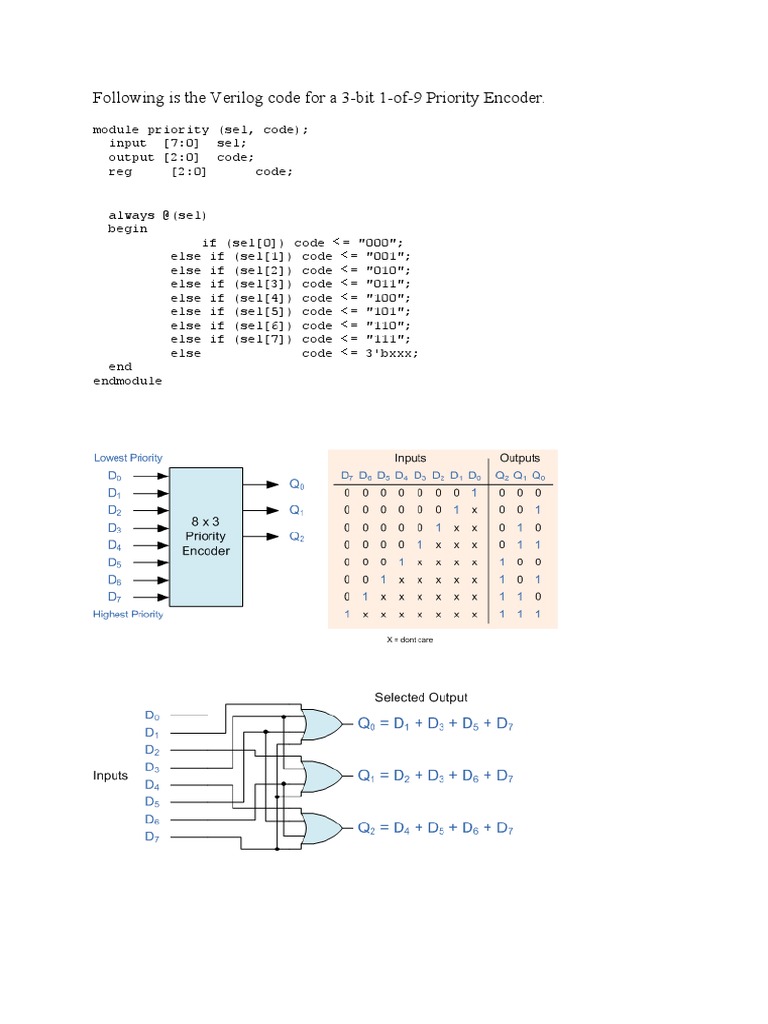

Following Is The Verilog Code For A 3 Bit 1 Of 9 Priority Encoder Pdf The document discusses various verilog code modules for digital logic components like parity encoder, decoder, adder, comparator and shift registers. it provides structural, behavioral and dataflow modeling examples for these components in verilog with brief explanations. What is priority encoder? a priority encoder is a digital circuit which encodes the input signals according to the priority. it has several input lines; its output line shows the binary code of set active input line considered to be the highest priority.

Verilog Code For Parity Encoder Parity encoder: parity encoder is a combinational circuit,which is used to find the even and odd parity from the binary sequence. in this code,the data flow statements are used for genrate a parity encoder. To overcome the disadvantages of binary encoders, priority encoders were developed that work based on the highest priority input. this article gives a brief description of a priority encoder along with its applications. Contribute to 2200040225 verilog for parity encoder development by creating an account on github. This page contains verilog tutorial, verilog syntax, verilog quick reference, pli, modeling memory and fsm, writing testbenches in verilog, lot of verilog examples and verilog in one day tutorial.

Verilog Code For Parity Encoder Contribute to 2200040225 verilog for parity encoder development by creating an account on github. This page contains verilog tutorial, verilog syntax, verilog quick reference, pli, modeling memory and fsm, writing testbenches in verilog, lot of verilog examples and verilog in one day tutorial. Now, we will learn how to design a 4:2 priority encoder using different modeling styles in verilog. this is virtually the lowest abstraction layer, which is used by designers for implementing the lowest level modules, as the switch level modeling isn’t that common. Various encoders can be designed like decimal to binary encoders, octal to binary encoders, decimal to bcd encoders, etc. an encoder basically shrinks receiving many input data lines to the output lines. this is helpful in reducing input data lines for further processing. Learn how to implement a priority encoder in verilog using if else and case statements. step by step guide with examples to encode the highest priority active input efficiently. The document provides verilog modeling implementations for various digital circuits including encoders, parity generators, comparators, adders, and multipliers.

Verilog Priority Encoder Now, we will learn how to design a 4:2 priority encoder using different modeling styles in verilog. this is virtually the lowest abstraction layer, which is used by designers for implementing the lowest level modules, as the switch level modeling isn’t that common. Various encoders can be designed like decimal to binary encoders, octal to binary encoders, decimal to bcd encoders, etc. an encoder basically shrinks receiving many input data lines to the output lines. this is helpful in reducing input data lines for further processing. Learn how to implement a priority encoder in verilog using if else and case statements. step by step guide with examples to encode the highest priority active input efficiently. The document provides verilog modeling implementations for various digital circuits including encoders, parity generators, comparators, adders, and multipliers.

Comments are closed.