Solved 5 1 Write A Structural Verilog Module Corresponding Chegg

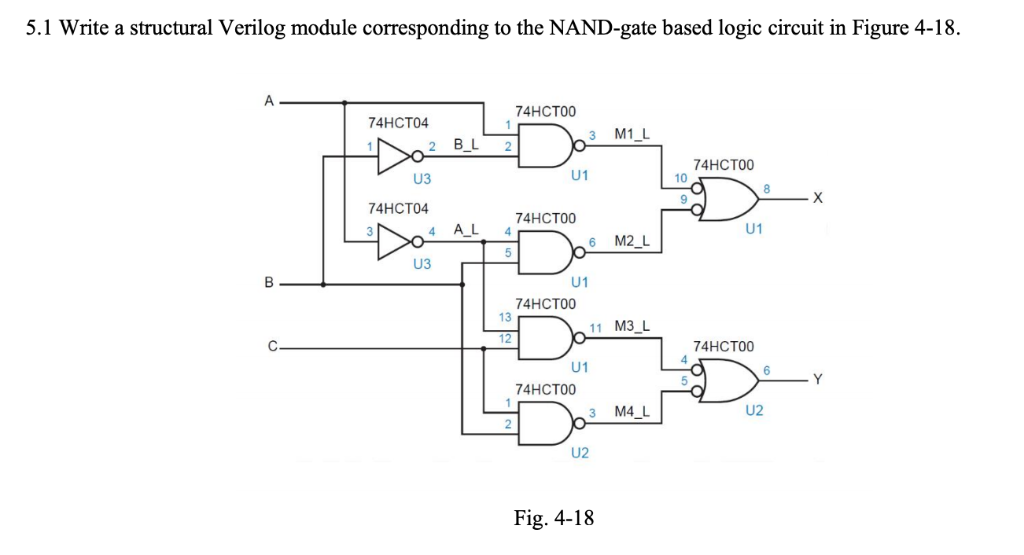

Solved 5 1 Write A Structural Verilog Module Corresponding Chegg Our expert help has broken down your problem into an easy to learn solution you can count on. here’s the best way to solve it. if any …. Verilog 2001 has a syntax option as part of an ansi style module declarations in the maj module of ic signals on its pins uts and outputs of the nals on its pins. the pin numbers are written near the corresponding outputs of the standard logic symbol, as shown in figure 4 18.

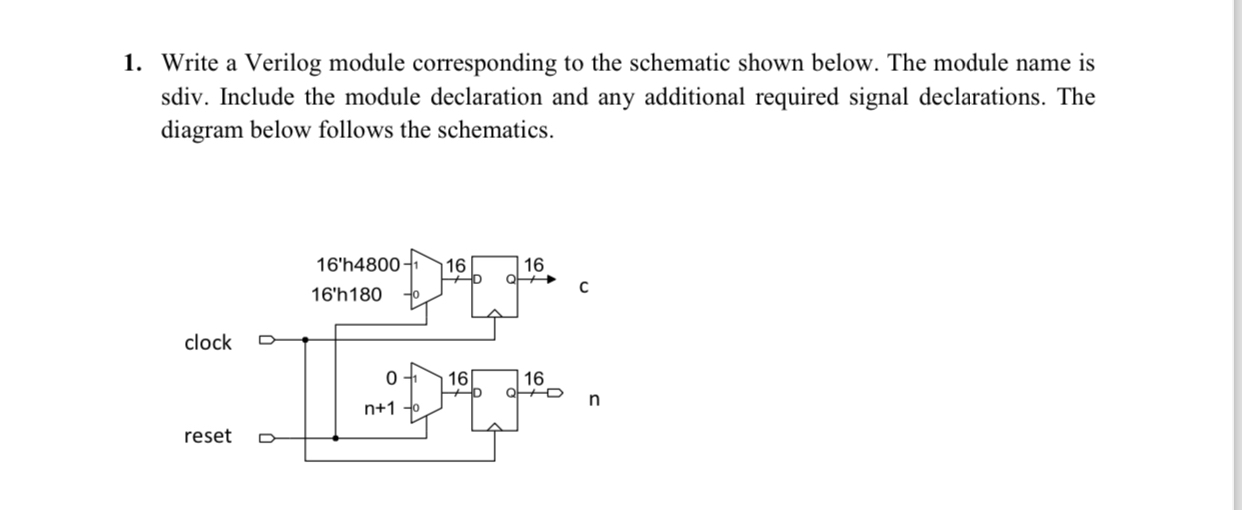

Write A Verilog Module Corresponding To The Schematic Chegg Examples show codes for a 2 input or gate, 2 1 multiplexer, and a combinational circuit. exercises have students write code for a given circuit and draw the logic diagram from given code. This verilog documentation will focus on the structural level of description because it is efficient to code, yet offers a predictable mapping to hardware in the hands of a skilled user. After switch level modeling, structural modeling is the lowest level of abstraction in verilog. it is also called gate level modeling because we only describe a hardware in logic gates and their inteconnections. Learn structural design with verilog. covers modeling, operators, flip flops, state machines, and style guidelines. ideal for college level electrical engineering.

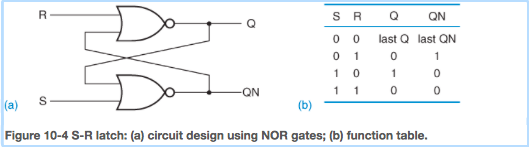

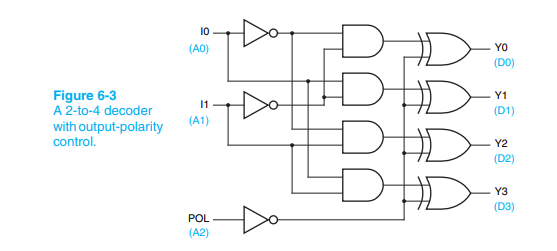

Solved 10 12 Write A Structural Verilog Module Chegg After switch level modeling, structural modeling is the lowest level of abstraction in verilog. it is also called gate level modeling because we only describe a hardware in logic gates and their inteconnections. Learn structural design with verilog. covers modeling, operators, flip flops, state machines, and style guidelines. ideal for college level electrical engineering. Part a — module anatomy & instantiation 1. comments in verilog verilog supports two styles of comments, both functionally identical but with a critical behavioral difference that regularly traps engineers. Write a structural style verilog module vr2to4decp s corresponding to the 2 to 4 binary decoder with polarity control shown in figure 6 3. use individual signal names as in the logic diagram, not vectors. In gate level modelling, we use primitive gates to model a circuit depending on its schematic diagram. this is part – 1 of tutorial on structural modelling. these gates can have ‘n’ inputs, and one output. the truth tables of the above gates are given below. In this exercise you will create the structural systemverilog description of four logic functions. note that you must use structural systemverilog rather than dataflow systemverilog to complete this assignment.

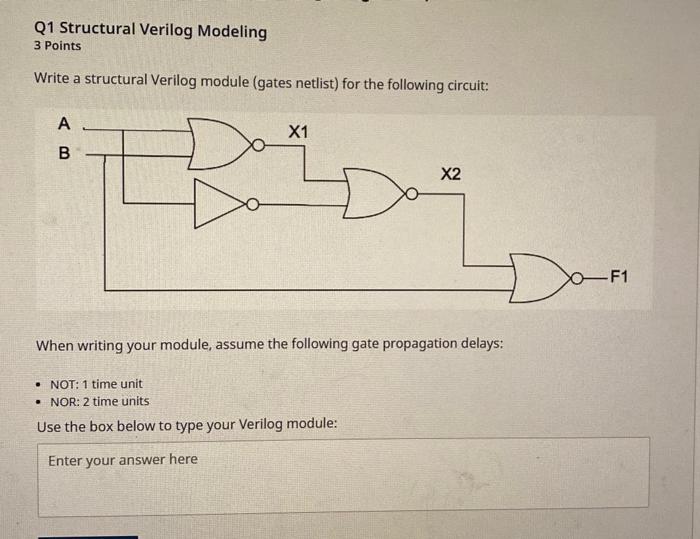

Solved Q1 Structural Verilog Modeling 3 Points Write A Chegg Part a — module anatomy & instantiation 1. comments in verilog verilog supports two styles of comments, both functionally identical but with a critical behavioral difference that regularly traps engineers. Write a structural style verilog module vr2to4decp s corresponding to the 2 to 4 binary decoder with polarity control shown in figure 6 3. use individual signal names as in the logic diagram, not vectors. In gate level modelling, we use primitive gates to model a circuit depending on its schematic diagram. this is part – 1 of tutorial on structural modelling. these gates can have ‘n’ inputs, and one output. the truth tables of the above gates are given below. In this exercise you will create the structural systemverilog description of four logic functions. note that you must use structural systemverilog rather than dataflow systemverilog to complete this assignment.

Solved Write A Structural Style Verilog Module Vr2to4decp S In gate level modelling, we use primitive gates to model a circuit depending on its schematic diagram. this is part – 1 of tutorial on structural modelling. these gates can have ‘n’ inputs, and one output. the truth tables of the above gates are given below. In this exercise you will create the structural systemverilog description of four logic functions. note that you must use structural systemverilog rather than dataflow systemverilog to complete this assignment.

Comments are closed.