Verilog Modules Using Code Only

Verilog Modules Siliconvlsi Instead of using the schematic capture, learn how to connect together multiple verilog modules into a single module. thanks to everyone who've stuck around for this series!. Learn how to define and instantiate modules in verilog, create hierarchical designs, and manage interconnections for large digital systems.

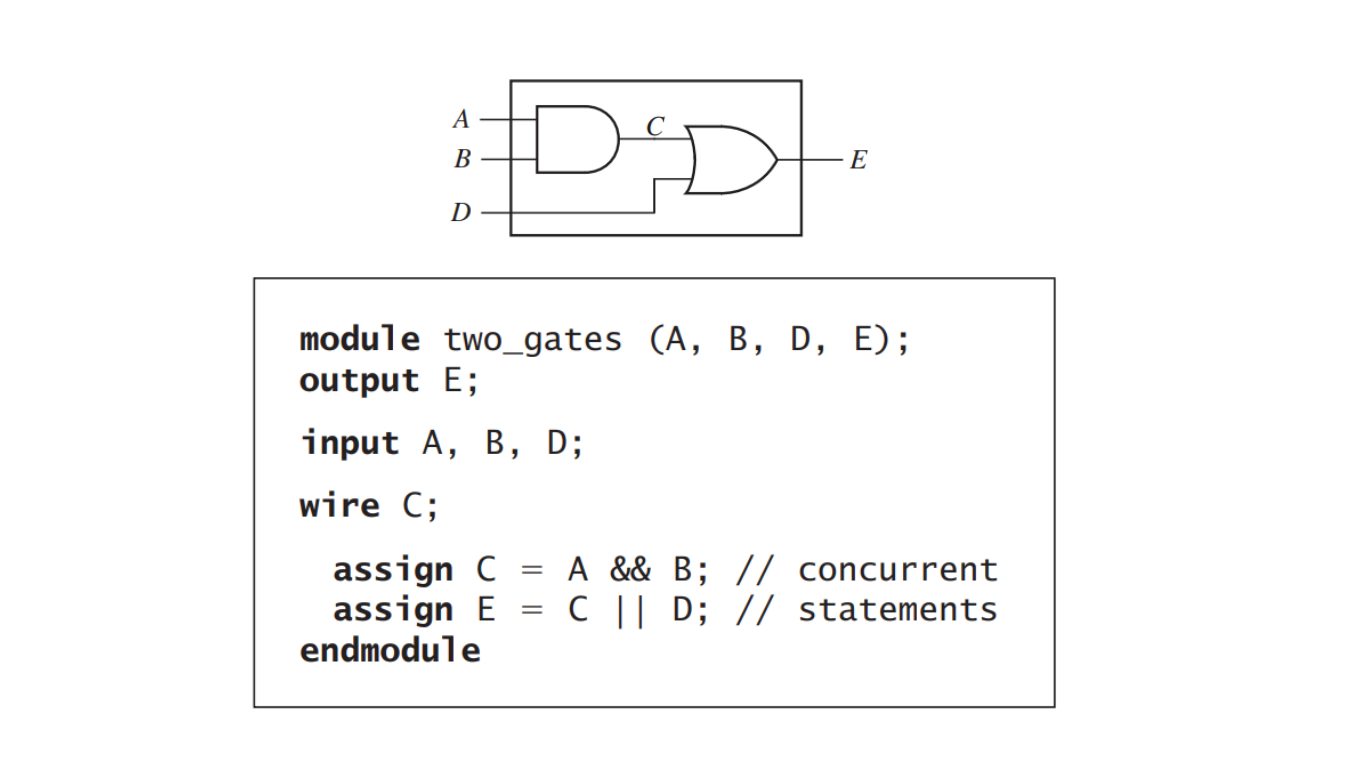

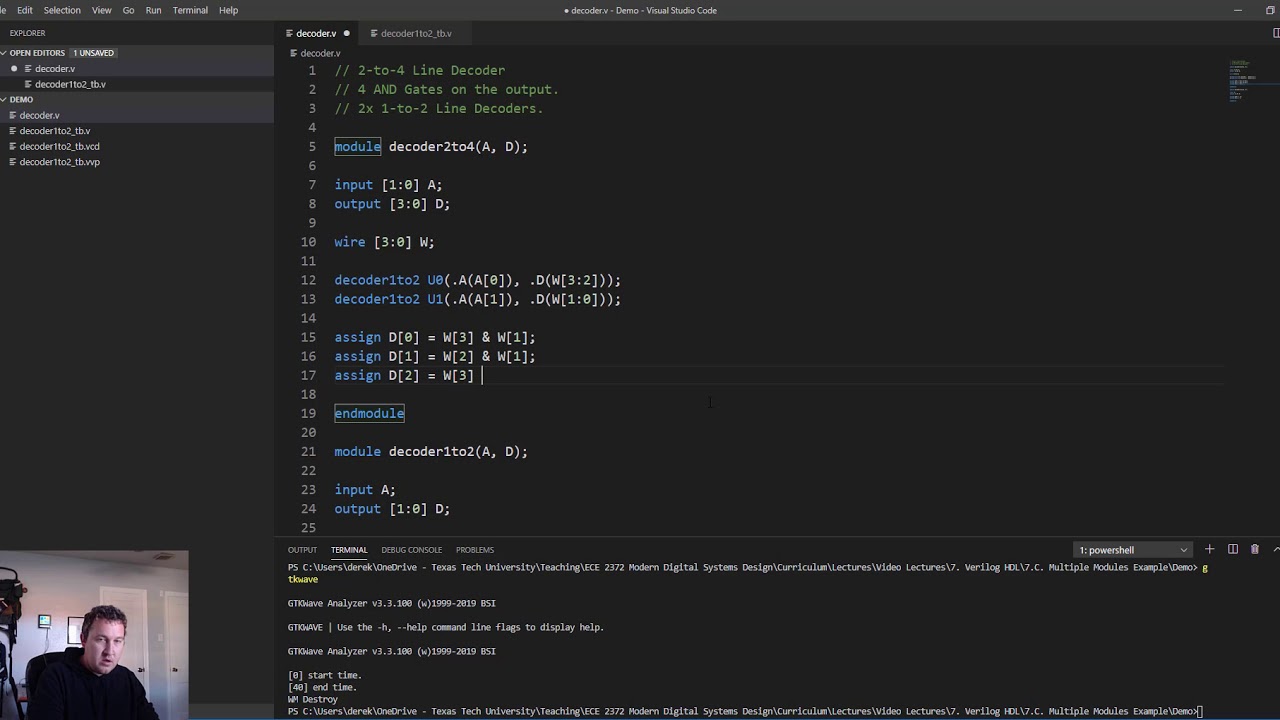

04 Verilog Codes For Basic Components 2021f Download Free Pdf Why it's problematic: verilog requires all executable code (assign statements, always blocks, initial blocks) to be encapsulated within module endmodule boundaries. Learn how modules are used in verilog to structure designs and how this relates to the underlying hardware which is being described. You should edit the question to add a followup that shows the complete code for the second module that you're now using, along with the exact error message that the tool is giving you. Learn the basics of verilog module, their syntax, purpose, and how to use top level modules and testbenches in digital design.

Github Jstraughan21 Verilog Modules Collection Of Individual Verilog You should edit the question to add a followup that shows the complete code for the second module that you're now using, along with the exact error message that the tool is giving you. Learn the basics of verilog module, their syntax, purpose, and how to use top level modules and testbenches in digital design. Modules can be instantiated multiple times within a larger verilog design, facilitating the creation of complex digital circuits by connecting modules together in a hierarchical fashion. Even though this one was not built on a breadboard, it has the functionalities of his computer and modelled using verilog hdl. this project was developed as a mini project in digital systems course in my 3rd semester at iit palakkad. As an rtl design engineer, i’ve spent countless hours crafting verilog code for everything from simple counters to complex state machines. in this post, i’ll walk you through the essentials of writing clean, functional verilog code, with practical tips and snippets to get you started. Ports of an instantiated module can be connected to signals referenced in the module’s declaration assuming they are in the same order but this is dangerous so don’t do it.

Using Library Modules Verilog Pdf Computer Science Digital Modules can be instantiated multiple times within a larger verilog design, facilitating the creation of complex digital circuits by connecting modules together in a hierarchical fashion. Even though this one was not built on a breadboard, it has the functionalities of his computer and modelled using verilog hdl. this project was developed as a mini project in digital systems course in my 3rd semester at iit palakkad. As an rtl design engineer, i’ve spent countless hours crafting verilog code for everything from simple counters to complex state machines. in this post, i’ll walk you through the essentials of writing clean, functional verilog code, with practical tips and snippets to get you started. Ports of an instantiated module can be connected to signals referenced in the module’s declaration assuming they are in the same order but this is dangerous so don’t do it.

How To Implement Verilog Code With Small Modules Stack Overflow As an rtl design engineer, i’ve spent countless hours crafting verilog code for everything from simple counters to complex state machines. in this post, i’ll walk you through the essentials of writing clean, functional verilog code, with practical tips and snippets to get you started. Ports of an instantiated module can be connected to signals referenced in the module’s declaration assuming they are in the same order but this is dangerous so don’t do it.

Source Code File Verilog Verilog Parameters

Comments are closed.