Modules Verilog Fundamentals

Basics In Verilog Pdf Computer Science Computing Hierarchical design: verilog enables hierarchical design, which allows for the creation of complex systems by breaking them down into smaller, manageable modules. Welcome to our free digital vlsi (dv) course! in this video, we cover the fundamentals of verilog, focusing on: modules in verilog – the building blocks of every design more.

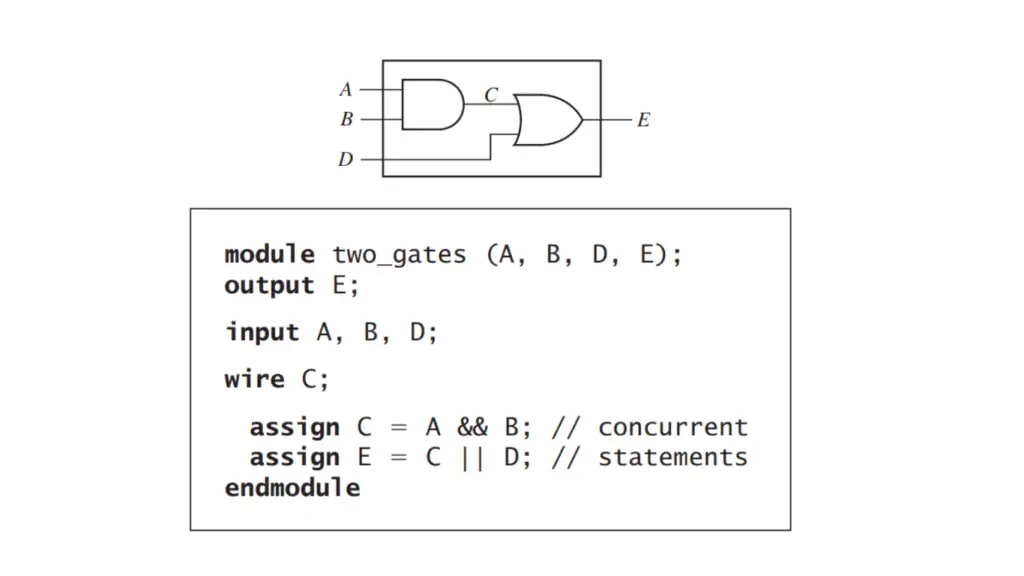

Verilog Tutorial Part 1 Pdf Learn how to define and instantiate modules in verilog, create hierarchical designs, and manage interconnections for large digital systems. This chapter introduces the essential elements of verilog, from the primary design unit—the module—to the data types that hold values and the operators that manipulate them. Unit 1 verilog as hdl verilog has a variety of constructs as part of it. all are aimed at providing a functionally tested and a verified design description for the target fpga or asic. A module is a block of verilog code that implements a certain functionality. modules can be embedded within other modules and a higher level module can communicate with its lower level modules using their input and output ports.

Basics Of Verilog Session 1 Pdf Hardware Description Language Unit 1 verilog as hdl verilog has a variety of constructs as part of it. all are aimed at providing a functionally tested and a verified design description for the target fpga or asic. A module is a block of verilog code that implements a certain functionality. modules can be embedded within other modules and a higher level module can communicate with its lower level modules using their input and output ports. Learn the basics of verilog module, their syntax, purpose, and how to use top level modules and testbenches in digital design. 1 fundamentals verilog fa fa fa fa module adder( input [3:0] a, b, output cout, output [3:0] s ); wire c0, c1, c2; fa fa0( a[0], b[0], 1’b0, c0, s[0] ); fa fa1( a[1], b[1], c0, c1, s[1] ); fa fa2( a[2], b[2], c1, c2, s[2] ); fa fa3( a[3], b[3], c2, cout, s[3] );. This course is your introduction to verilog, the essential hardware description language used in digital design. through a combination of theory and hands on practice, you'll learn the fundamentals of verilog coding, including logic gates, data types, and procedural statements. Learn how modules are used in verilog to structure designs and how this relates to the underlying hardware which is being described.

Github Kirkster96 Verilog Fundamentals Learn the basics of verilog module, their syntax, purpose, and how to use top level modules and testbenches in digital design. 1 fundamentals verilog fa fa fa fa module adder( input [3:0] a, b, output cout, output [3:0] s ); wire c0, c1, c2; fa fa0( a[0], b[0], 1’b0, c0, s[0] ); fa fa1( a[1], b[1], c0, c1, s[1] ); fa fa2( a[2], b[2], c1, c2, s[2] ); fa fa3( a[3], b[3], c2, cout, s[3] );. This course is your introduction to verilog, the essential hardware description language used in digital design. through a combination of theory and hands on practice, you'll learn the fundamentals of verilog coding, including logic gates, data types, and procedural statements. Learn how modules are used in verilog to structure designs and how this relates to the underlying hardware which is being described.

Verilog Modules Siliconvlsi This course is your introduction to verilog, the essential hardware description language used in digital design. through a combination of theory and hands on practice, you'll learn the fundamentals of verilog coding, including logic gates, data types, and procedural statements. Learn how modules are used in verilog to structure designs and how this relates to the underlying hardware which is being described.

Github Nikee2021 Basic Verilog Modules

Comments are closed.