Tsmc Chip On Wafer On Substrate Cowos Packaging Is A Key Development

Tsmc Boosts Tools For Chip On Wafer On Substrate Packaging Tsmc’s chip on wafer on substrate with silicon interposer (cowos ® s) provides best in class package technology for ultra high performance computing applications, such as artificial intelligence (ai) and supercomputing. Taiwan semiconductor manufacturing company (nyse: tsm) is aggressively expanding its chip on wafer on substrate (cowos) advanced packaging capacity, aiming for a 33% increase by 2026 to satisfy an insatiable global appetite for ai silicon.

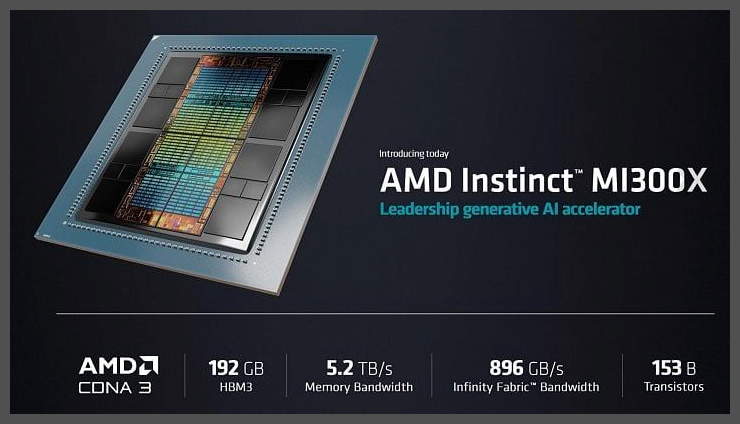

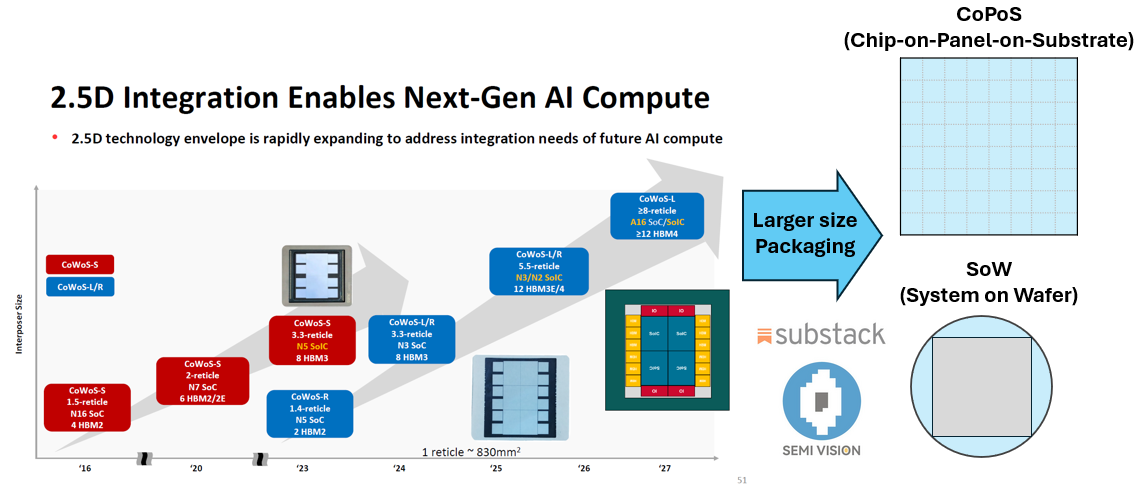

Tsmc Chip On Wafer On Substrate Cowos Packaging Is A Key Development Tsmc has developed several versions to support diverse applications: cowos® (chip on wafer on substrate) is a 2.5d advanced packaging technology developed by tsmc that allows multiple dies—including logic, memory, and analog ics—to be integrated side by side on a high density silicon interposer. Tsmc’s cowos advanced packaging capacity is currently a matter of intense interest for major technology companies worldwide. we’ve been closely tracking these developments, and the following insights are drawn from an expert transcript shared by an investor in the semiconductor space. In this article, we provide a comprehensive walkthrough of cowos technology, from its process flow and key architectural elements to real world use cases and future roadmap. what is cowos? cowos, short for chip on wafer on substrate, is an advanced 2.5d packaging technology pioneered by tsmc. Tsmc plans to expand eight cowos facilities in the short term, including facilities at chiayi science park and acquired innolux locations. 5 semiconductor equipment suppliers confirm that tsmc and non tsmc players including ase, amkor, and umc are accelerating advanced packaging capacity expansion.

Tsmc Copos Packaging Technology Next Gen Panel Level Solution For Ai Chips In this article, we provide a comprehensive walkthrough of cowos technology, from its process flow and key architectural elements to real world use cases and future roadmap. what is cowos? cowos, short for chip on wafer on substrate, is an advanced 2.5d packaging technology pioneered by tsmc. Tsmc plans to expand eight cowos facilities in the short term, including facilities at chiayi science park and acquired innolux locations. 5 semiconductor equipment suppliers confirm that tsmc and non tsmc players including ase, amkor, and umc are accelerating advanced packaging capacity expansion. By developing a pcb motherboard with high integration and high signal transmission performance, cowop effectively reduces the material and manufacturing costs of the packaging substrate while maintaining the core cow (chip on wafer) stacking architecture. Looking toward 2027, tsmc will launch cowos l. first up are large n3 node chiplets, followed by n2 node tiles, multiple i o dies, and up to a dozen hbm3e or hbm4 stacks—all housed within a 5.5× reticle ceiling. Using its n16 finfet technology, the company embeds monolithic power management ics and on wafer inductors into the cowos l substrate, allowing power to be routed efficiently through the. Cowos technology is an advanced packaging solution developed by tsmc that integrates multiple chips or dies onto a single silicon interposer, which is then placed on a substrate. this technique enables the creation of highly integrated systems with enhanced performance metrics.

Comments are closed.