Tsmc Copos Packaging Technology Next Gen Panel Level Solution For Ai Chips

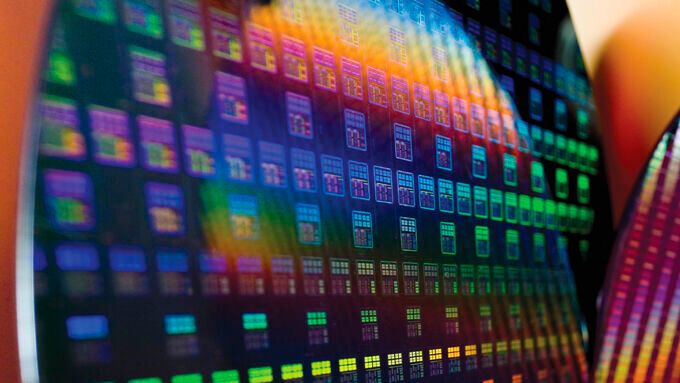

Tsmc Nears Finalization Of Panel Level Chip Packaging For Nvidia Discover how tsmc is accelerating copos (chip on panel on substrate) development to meet growing ai and hpc chip demands. learn about its panel level packaging breakthrough, cost efficiency, and roadmap through 2029. In response to the need for more space, tsmc has unveiled plans for copos, or "chips on panel on substrate," which could expand substrate dimensions to 310 × 310 mm and beyond. by shifting from round wafers to rectangular panels, copos offers more than five times the usable area.

Samsung Reportedly Ahead Of Tsmc With Next Gen Panel Level Packaging Copos is essentially a panel based upgrade of cowos, arranging chips on large square substrates instead of traditional round silicon interposers. this change not only effectively increases. Copos builds upon tsmc’s existing cowos (chip on wafer on substrate) technology, which has been integral to ai chip manufacturing. by adopting a panel level approach, copos aims to overcome the limitations of wafer based packaging, such as size constraints and yield issues. According to commercial times, tsmc’s copos (chip on panel on substrate) pilot line has already begun tool deliveries to r&d teams in february, with the full line on track for completion by june. By switching to panel based packaging, tsmc dramatically expands usable area per unit, clearing bottlenecks and making it much easier to scale production of large footprint ai components.

Samsung Reportedly Ahead Of Tsmc With Next Gen Panel Level Packaging According to commercial times, tsmc’s copos (chip on panel on substrate) pilot line has already begun tool deliveries to r&d teams in february, with the full line on track for completion by june. By switching to panel based packaging, tsmc dramatically expands usable area per unit, clearing bottlenecks and making it much easier to scale production of large footprint ai components. Advanced micro devices (nasdaq: amd) and broadcom (nasdaq: avgo) are reportedly in deep discussions with tsmc to utilize panel level packaging for their future instinct and custom ai silicon, respectively. Tsmc unveils its next gen copos packaging, vastly expanding available space for advanced artificial intelligence hardware and enabling breakthroughs in chip integration. In the future, tsmc will form a multi tiered advanced packaging portfolio with cowos (s r l) as the core, copos as the next gen high end flagship, and cowop as the cost performance balance solution – fully meeting the diverse packaging needs of ai, hpc, edge computing and other sectors. Copos is designed to build on two of tsmc’s packaging systems: cowos r, typically used for broadcom products, and cowos l, developed for clients like nvidia and amd. unlike traditional cowos which relies on circular wafers, copos uses rectangular panels measuring 310x310mm.

Tsmc Introduces Copos Packaging With Massive 310 310 Mm Panels Epium Advanced micro devices (nasdaq: amd) and broadcom (nasdaq: avgo) are reportedly in deep discussions with tsmc to utilize panel level packaging for their future instinct and custom ai silicon, respectively. Tsmc unveils its next gen copos packaging, vastly expanding available space for advanced artificial intelligence hardware and enabling breakthroughs in chip integration. In the future, tsmc will form a multi tiered advanced packaging portfolio with cowos (s r l) as the core, copos as the next gen high end flagship, and cowop as the cost performance balance solution – fully meeting the diverse packaging needs of ai, hpc, edge computing and other sectors. Copos is designed to build on two of tsmc’s packaging systems: cowos r, typically used for broadcom products, and cowos l, developed for clients like nvidia and amd. unlike traditional cowos which relies on circular wafers, copos uses rectangular panels measuring 310x310mm.

Panel Level Packaging At Tsmc First Copos Pilot Line In 2026 Mass In the future, tsmc will form a multi tiered advanced packaging portfolio with cowos (s r l) as the core, copos as the next gen high end flagship, and cowop as the cost performance balance solution – fully meeting the diverse packaging needs of ai, hpc, edge computing and other sectors. Copos is designed to build on two of tsmc’s packaging systems: cowos r, typically used for broadcom products, and cowos l, developed for clients like nvidia and amd. unlike traditional cowos which relies on circular wafers, copos uses rectangular panels measuring 310x310mm.

Comments are closed.