Source Code Error Detection In High Level Synthesis Functional Verification

Source Code Error Detection Hls Based Functional Verification A dynamic functional verification method that compares untimed simulations versus timed simulations for synthesizable [high level synthesis (hls)] behavioral descriptions (ansi c) is presented in this paper. This work defines a methodology to automatically detect and isolate bugs in parallel circuits generated with hls.

Ieee 2016 Vlsi Source Code Error Detection In High Level Synthesis Funct A way to verify a high level synthesis system automatically, called satya, maps an algorithmic description to a logic circuit description and compares descriptions to detect semantic errors and identify the cause of those errors. Explore the article titled source code error detection in high level synthesis functional verification from ijirt volume 4, issue 1. this study evaluates the effectiveness of teaching programs on waste management knowledge among women. Our proposed method reports any simulation mismatches and accurately pinpoints any discrepancies between the functional software (sw) simulation and the timed simulation at the original behavioral description (source code). Our proposed method reports any simulation mismatches and accurately pinpoints any discrepancies between the functional software (sw) simulation and the timed simulation at the original behavioral description (source code).

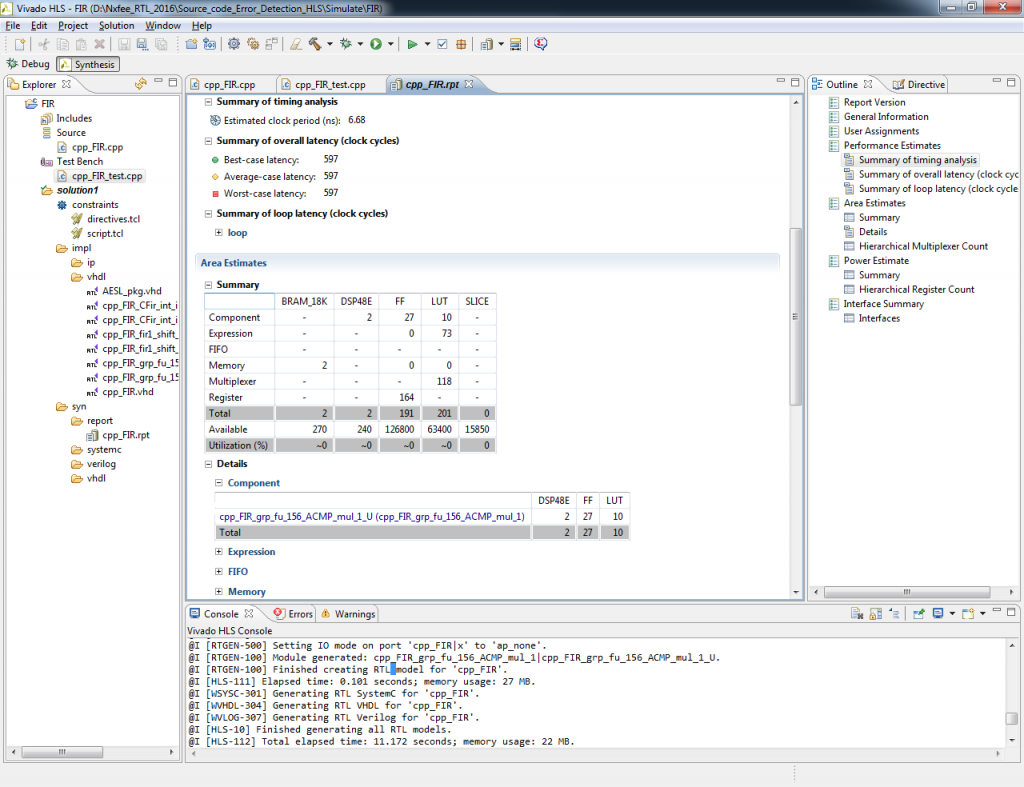

Figure 1 From Source Code Error Detection In High Level Synthesis Our proposed method reports any simulation mismatches and accurately pinpoints any discrepancies between the functional software (sw) simulation and the timed simulation at the original behavioral description (source code). Our proposed method reports any simulation mismatches and accurately pinpoints any discrepancies between the functional software (sw) simulation and the timed simulation at the original behavioral description (source code). Bibliographic details on source code error detection in high level synthesis functional verification. In this proposed system, a complete automated verification flow for synthesizable behavioral descriptions in order to detect where in the source code mismatches between the original untimed simulation and the timed synthesized design occur.

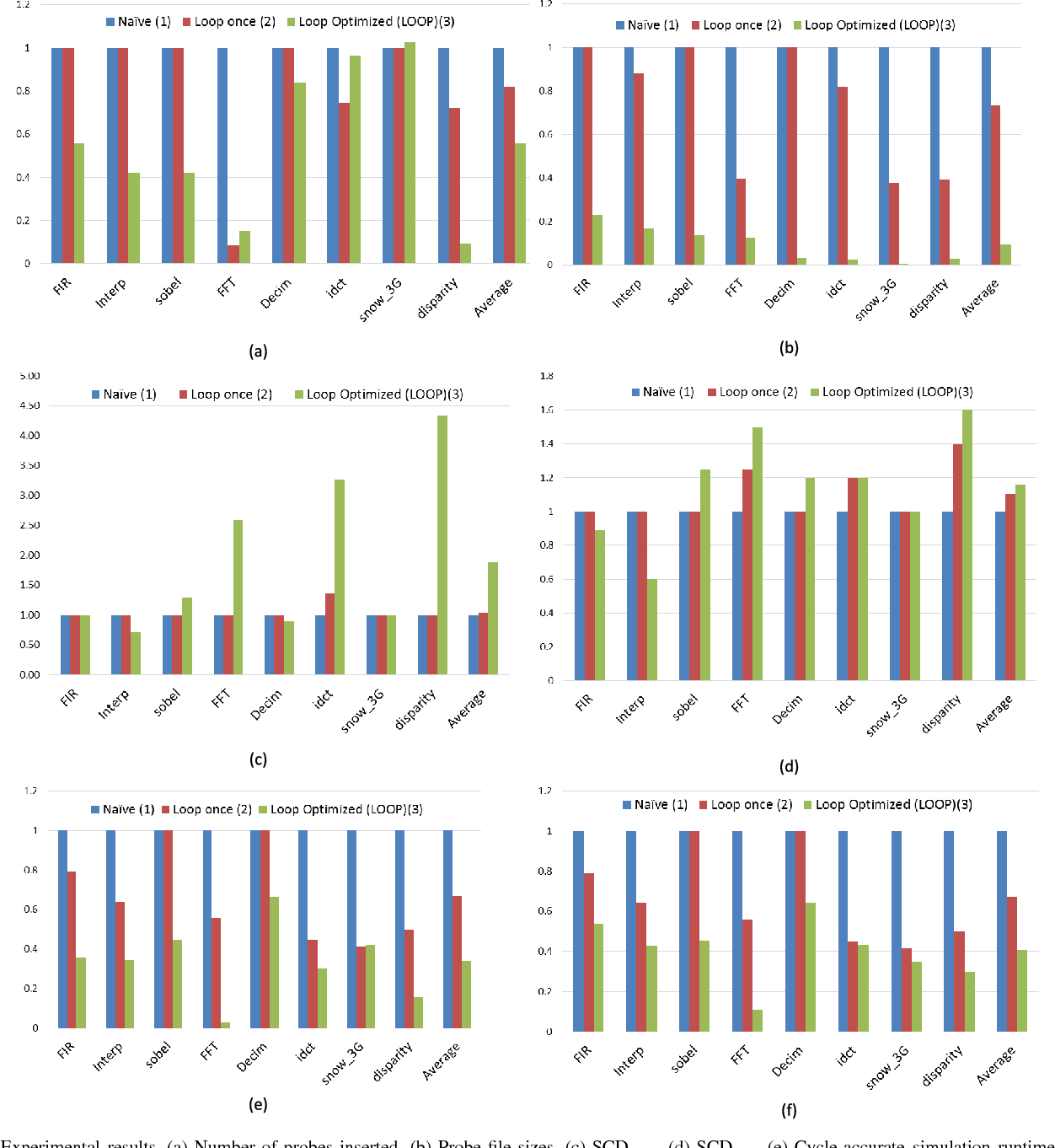

Figure 10 From Source Code Error Detection In High Level Synthesis Bibliographic details on source code error detection in high level synthesis functional verification. In this proposed system, a complete automated verification flow for synthesizable behavioral descriptions in order to detect where in the source code mismatches between the original untimed simulation and the timed synthesized design occur.

Comments are closed.