Solved Practice Problem Single Cycle Multi Cycle And Chegg

Chegg Pdf Our expert help has broken down your problem into an easy to learn solution you can count on. How much time on multi cycle? to answer this, we need to know (1) the clock cycle length for the multi cycle implementation, and (2) how many instructions of each type are executed.

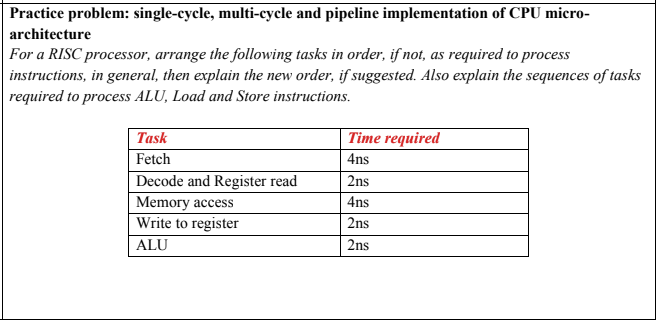

Solved Practice Problem Single Cycle Multi Cycle And Chegg There are two kinds of datapath: single cycle datapath and multiple cycle datapath. this paper therefore plays the role of analyzing the differences between them which aids in enhancing instruction execution and system performance. Two important parameters control the performance of a processor: cycle time and cycles per instruction. there is an enduring trade‐off between these two parameters in the design process of microprocessors. Instead of a single cycle organization, we can use a multi cycle organization where each instruction takes multiple clock cycles, but one instruction finishes before another is fetched. Because there is no pipelining, the cycle time must allow an instruction to go through all stages in one cycle. the latency is the same as cycle time since it takes the instruction one cycle to go from the beginning of fetch to the end of writeback.

Chegg Sample Questions Solution Pdf Instead of a single cycle organization, we can use a multi cycle organization where each instruction takes multiple clock cycles, but one instruction finishes before another is fetched. Because there is no pipelining, the cycle time must allow an instruction to go through all stages in one cycle. the latency is the same as cycle time since it takes the instruction one cycle to go from the beginning of fetch to the end of writeback. This guide provides a detailed analysis of single cycle, multi cycle, and pipelined implementations, highlighting their differences, advantages, and trade offs. Keep the instructions earlier in the pipeline (later in the code) from progressing down the pipeline for a cycle (“bounce” them in place with write control signals). This summary of single cycle, multi cycle, and pipelined datapaths might be helpful. each datapath stage has a latency time associated with it, which is the minumum amount of time required for the stage to do its job. Only one stage of the cpu is active per cycle! an implementation technique in which multiple instructions are overlapped in execution. • can read a register source before even knowing what the instruction is! data mem. (it depends!) multiply down to see who wins! pipelining is the best of both worlds!!.

Comments are closed.