Single Cycle Multi Cycle And Pipelining

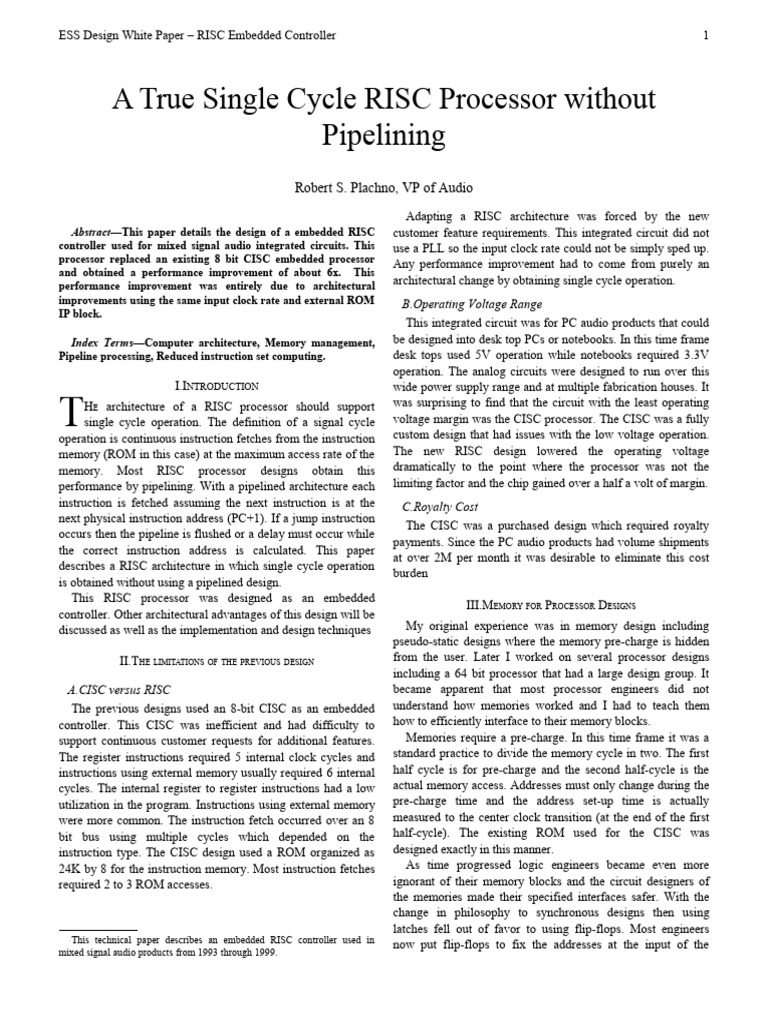

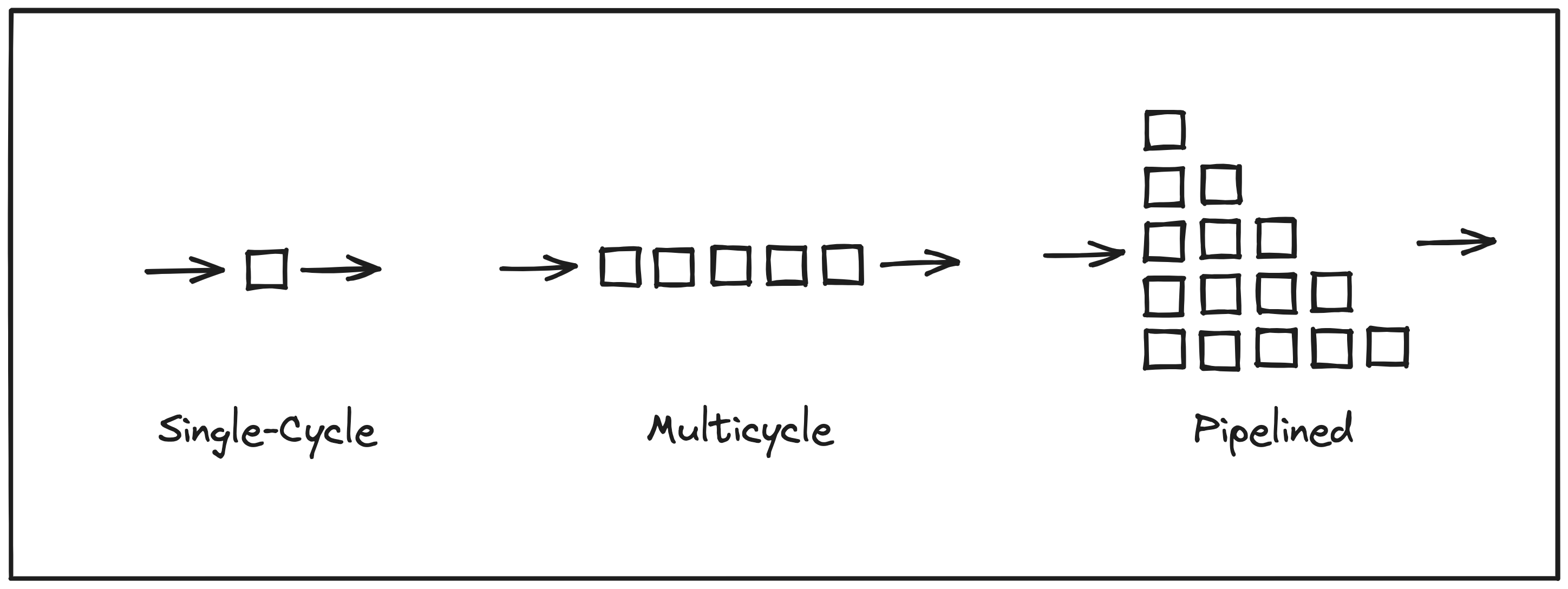

A True Single Cycle Risc Processor Without Pipelining Pdf Data paths are essential parts of the computer architecture that work in a processor to execute instructions. there are two basic categorized methodologies in datapath design: multi cycle data paths and pipeline data paths. There are three main architecture styles: single cycle, multi cycle, and pipelined. this is the most obvious approach to designing a processor: all the work for a single instruction is done in one cycle. because there’s a lot of work that needs to be done, the clock period is long.

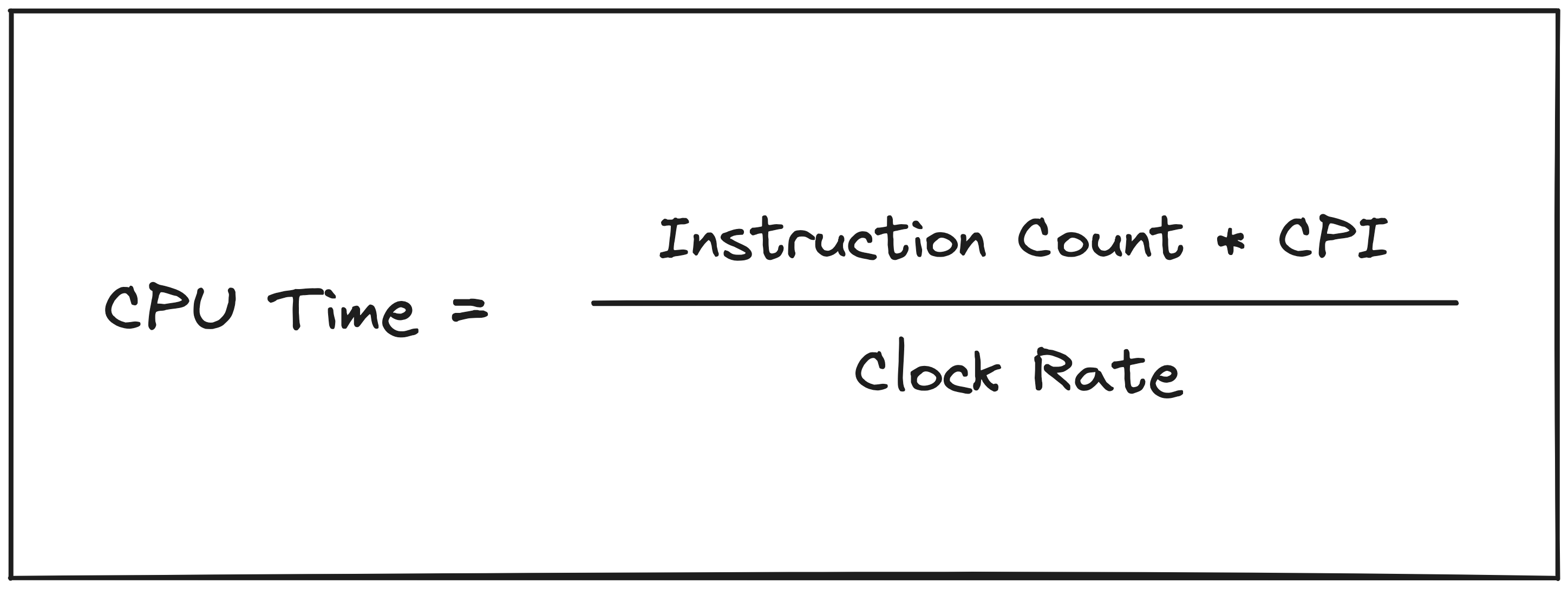

Single Cycle And Multicycle Do Not Describe Processor Performance How much time on multi cycle? to answer this, we need to know (1) the clock cycle length for the multi cycle implementation, and (2) how many instructions of each type are executed. Keep the instructions earlier in the pipeline (later in the code) from progressing down the pipeline for a cycle (“bounce” them in place with write control signals). Single cycle cpu design executes each instruction in a single clock cycle. there’s no module reuse. on the other hand, multi cycle cpu design allows instructions to be executed in short clock cycles. there’s module reuse. pipelined approach is a form of multi cycle cpu design. Think of it like shipping packages. in a single cycle model, every package waits for the longest delivery route before the truck can return. in a multi cycle model, packages move through shorter route segments, and trucks run more frequently. in practice, your instruction mix decides who wins.

Single Cycle And Multicycle Do Not Describe Processor Performance Single cycle cpu design executes each instruction in a single clock cycle. there’s no module reuse. on the other hand, multi cycle cpu design allows instructions to be executed in short clock cycles. there’s module reuse. pipelined approach is a form of multi cycle cpu design. Think of it like shipping packages. in a single cycle model, every package waits for the longest delivery route before the truck can return. in a multi cycle model, packages move through shorter route segments, and trucks run more frequently. in practice, your instruction mix decides who wins. Multiple cycle improves efficiency with shorter clock cycles but still processes one instruction at a time. pipeline achieves the highest throughput by overlapping multiple instructions in different stages simultaneously. You can make the cpi better and clock cycle worse by using multicycle, cpi worse but clock cycle better by using single cycle, but you can make both better by using pipelining. Several instructions can reach wb in a single cycle because of variable length instructions. this could cause a structural hazard if the cpu can only write one register per cycle. This guide provides a detailed analysis of single cycle, multi cycle, and pipelined implementations, highlighting their differences, advantages, and trade offs.

Github Farrukhaijaz Single Cycle Multi Cycle And Pipeline Arm Based Multiple cycle improves efficiency with shorter clock cycles but still processes one instruction at a time. pipeline achieves the highest throughput by overlapping multiple instructions in different stages simultaneously. You can make the cpi better and clock cycle worse by using multicycle, cpi worse but clock cycle better by using single cycle, but you can make both better by using pipelining. Several instructions can reach wb in a single cycle because of variable length instructions. this could cause a structural hazard if the cpu can only write one register per cycle. This guide provides a detailed analysis of single cycle, multi cycle, and pipelined implementations, highlighting their differences, advantages, and trade offs.

Comments are closed.