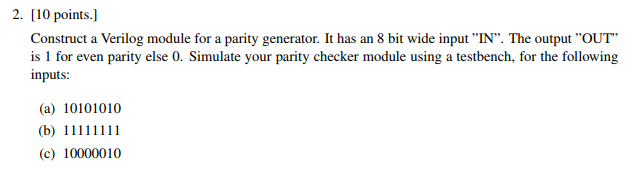

Solved 2 10 Points Construct A Verilog Module For A Chegg

Solved 2 10 Points Construct A Verilog Module For A Chegg P5. (10 points) given the circuit shown below: a. write the behavioral verilog module that corresponds to the circuit. b. write the structural verilog module that corresponds to the circuit. This verilog documentation will focus on the structural level of description because it is efficient to code, yet offers a predictable mapping to hardware in the hands of a skilled user.

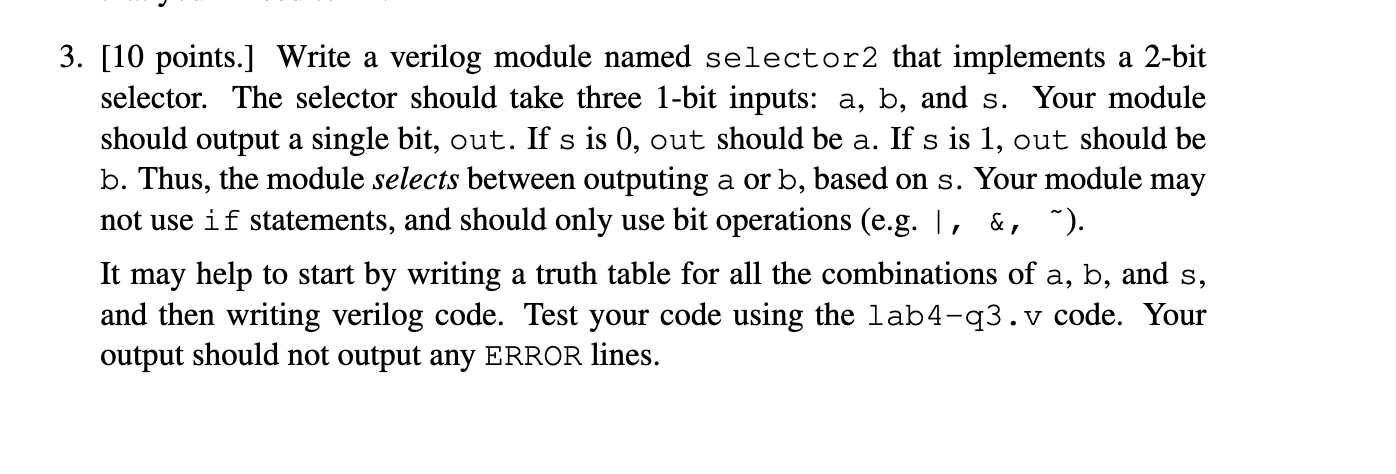

Solved 3 10 Points Write A Verilog Module Named Chegg Explore a mock exam for eece 2323 covering systemverilog module design and processor instruction execution, including coding tasks and explanations. Half adders are often used in hardware description languages, such as verilog, to simulate or design digital systems which then points out the importance of half adders in modern electronics. The assumption is that you already know how to create a project design in xilinx vivado and synthesize and implement that design objective: • synthesizing a verilog module • program nexsys 4 artix 7 fpga trainer board. They show two presumably costly oating point calculation modules, an adder and a multiplier. the goal of the problem is to use these modules over multiple cycles to perform a calculation.

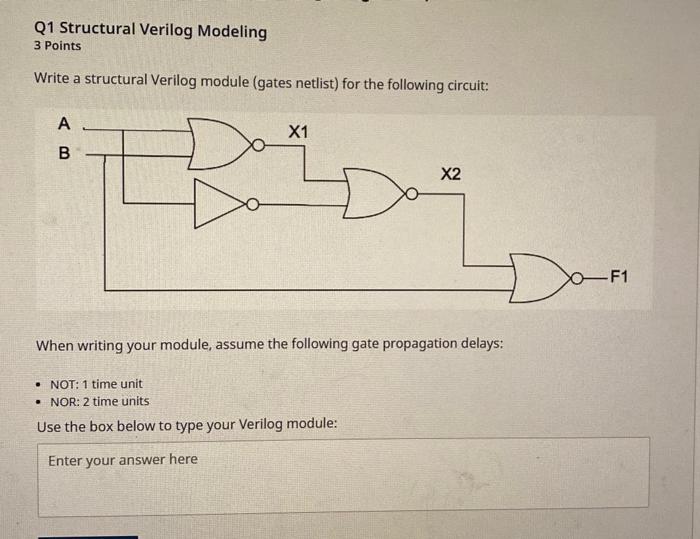

Solved Q1 Structural Verilog Modeling 3 Points Write A Chegg The assumption is that you already know how to create a project design in xilinx vivado and synthesize and implement that design objective: • synthesizing a verilog module • program nexsys 4 artix 7 fpga trainer board. They show two presumably costly oating point calculation modules, an adder and a multiplier. the goal of the problem is to use these modules over multiple cycles to perform a calculation. Instantiating a module in verilog is a fundamental concept for anyone working with digital design and hardware description languages. verilog modules allow designers to encapsulate functionality into reusable blocks, making it easier to manage complex designs and create hierarchical structures. instantiation is the process of creating an instance of a module within another module, enabling. Contribute to architam01 system verilog coding development by creating an account on github. Make sure the diagram shows what board peripherals each module is connected to. write the verilog implementation of pawn shop based on your block diagram. create a corresponding test bench pawn shop tb that verifies the behavior of your top level module. test and debug with modelsim, then load onto your board. We provide easy to understand tutorials for verilog, systemverilog, and uvm with 400 executable links.

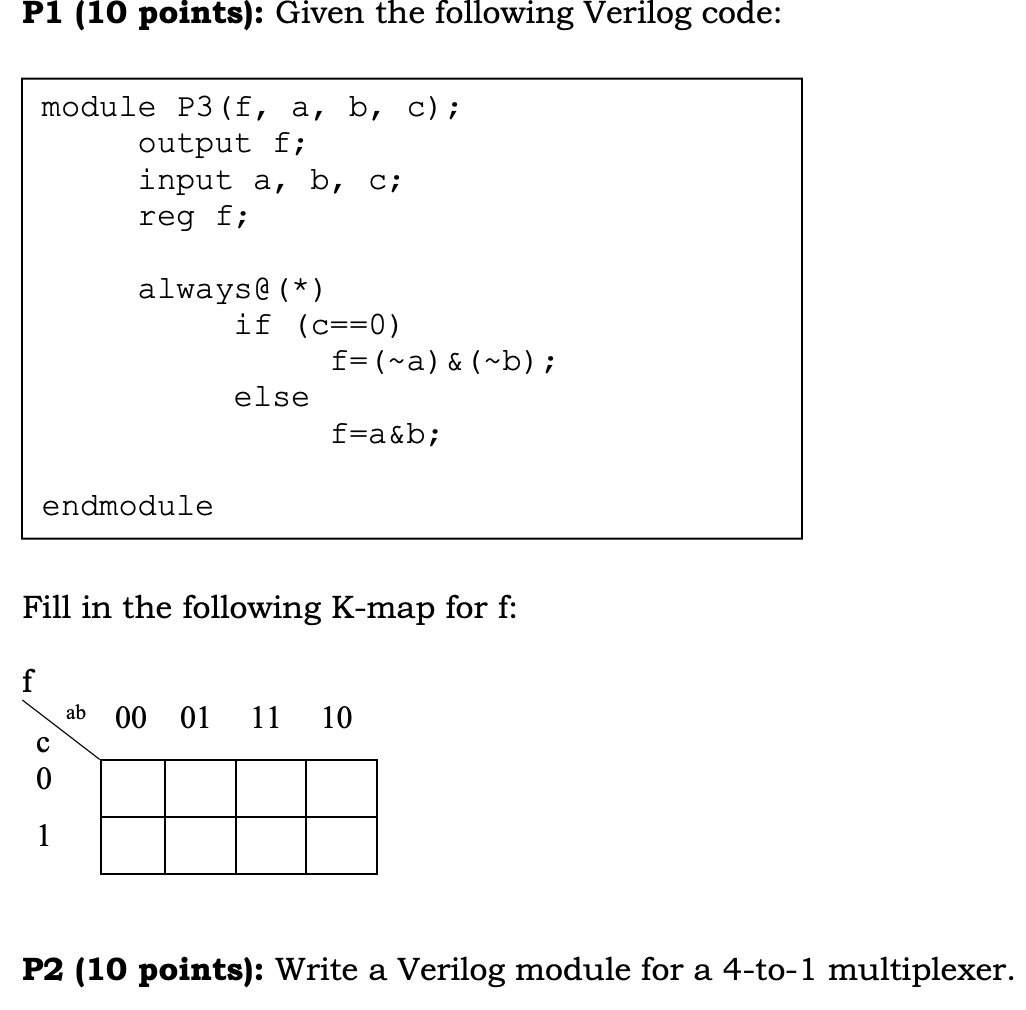

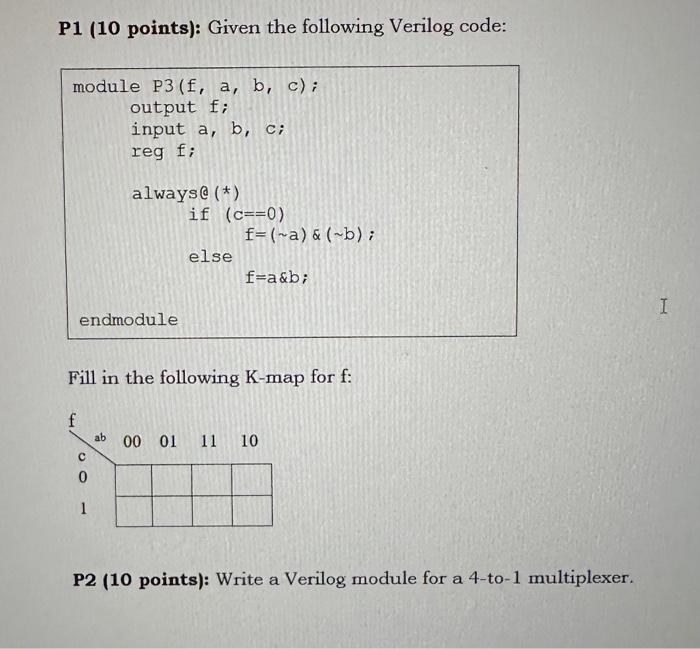

P1 10 Points Given The Following Verilog Code Chegg Instantiating a module in verilog is a fundamental concept for anyone working with digital design and hardware description languages. verilog modules allow designers to encapsulate functionality into reusable blocks, making it easier to manage complex designs and create hierarchical structures. instantiation is the process of creating an instance of a module within another module, enabling. Contribute to architam01 system verilog coding development by creating an account on github. Make sure the diagram shows what board peripherals each module is connected to. write the verilog implementation of pawn shop based on your block diagram. create a corresponding test bench pawn shop tb that verifies the behavior of your top level module. test and debug with modelsim, then load onto your board. We provide easy to understand tutorials for verilog, systemverilog, and uvm with 400 executable links.

P1 10 Points Given The Following Verilog Code Chegg Make sure the diagram shows what board peripherals each module is connected to. write the verilog implementation of pawn shop based on your block diagram. create a corresponding test bench pawn shop tb that verifies the behavior of your top level module. test and debug with modelsim, then load onto your board. We provide easy to understand tutorials for verilog, systemverilog, and uvm with 400 executable links.

Comments are closed.