Systemverilog Within Construct

Working Of Bind Construct Systemverilog Verification Academy This video explains the sva within construct as defined by the systemverilog language reference manual ieee 1800. Interpretation of the operator: the natural language meaning of 'within' might lead users to make incorrect assumptions about its behavior in sva. empty match scenarios: when the lhs sequence can terminate with an empty match, it introduces subtle behaviors that may not be immediately obvious.

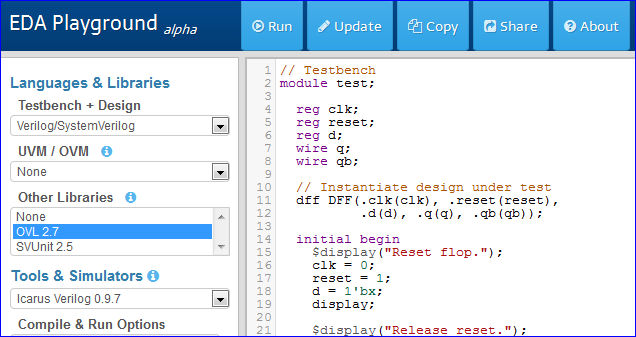

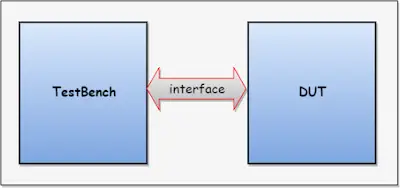

Working Of Bind Construct Systemverilog Verification Academy The bind construct in systemverilog allows you to attach code—such as assertions, covergroups, or even whole modules—to existing module or interface instances at elaboration time. By default in verilog a module declaration in itself doesn't do anything ( unless it's top tb ) , one needs to instantiate it for the logic defined within it to work . The within operator is used to express the containment of a sequence within another sequence and not operator for the non occurrence of the sequence. In systemverilog there are two kinds of assertions: immediate (assert) and concurrent (assert property). coverage statements (cover property) are concurrent and have the same syntax as concurrent assertions, as do assume property statements.

Systemverilog Interface Construct Verification Guide The within operator is used to express the containment of a sequence within another sequence and not operator for the non occurrence of the sequence. In systemverilog there are two kinds of assertions: immediate (assert) and concurrent (assert property). coverage statements (cover property) are concurrent and have the same syntax as concurrent assertions, as do assume property statements. A comprehensive tutorial on the systemverilog generate construct with a ton of useful examples. 1.1 what is an assertion? 1.2 why use systemverilog assertions (sva)?. Understanding the within operator i noticed from several posts that the within operator is frequently misunderstood, leading to its incorrect usage. this common misconception can result in errors. this paper clarifies the issues and provides solutions. Systemverilog assertions (sva) is essentially a language construct which provides a powerful alternate way to write constraints, checkers and cover points for your design.

Use Of Within Intersect And Other Operator Like Intersect In Sva A comprehensive tutorial on the systemverilog generate construct with a ton of useful examples. 1.1 what is an assertion? 1.2 why use systemverilog assertions (sva)?. Understanding the within operator i noticed from several posts that the within operator is frequently misunderstood, leading to its incorrect usage. this common misconception can result in errors. this paper clarifies the issues and provides solutions. Systemverilog assertions (sva) is essentially a language construct which provides a powerful alternate way to write constraints, checkers and cover points for your design.

Comments are closed.