Solution Synchronous Up Counter Using D Flipflop Studypool

Circuitverse 3 Bit Synchronous Up Counter Using D Flipflop Exp 11 Choose any historical image relevant to our time frame (1500 1865) that you think is interesting, significant, hilarious – choose whatever you’d like as long as it is an image dealing with our class. Design a 4 bit up counter that has two control inputs: cnt enables counting up, while clear synchronously resets the counter to all 0s: (a) using a parallel load register as a building block. (b) using flip flops and muxes by following the register design process of section 4.2. (component design problem.).

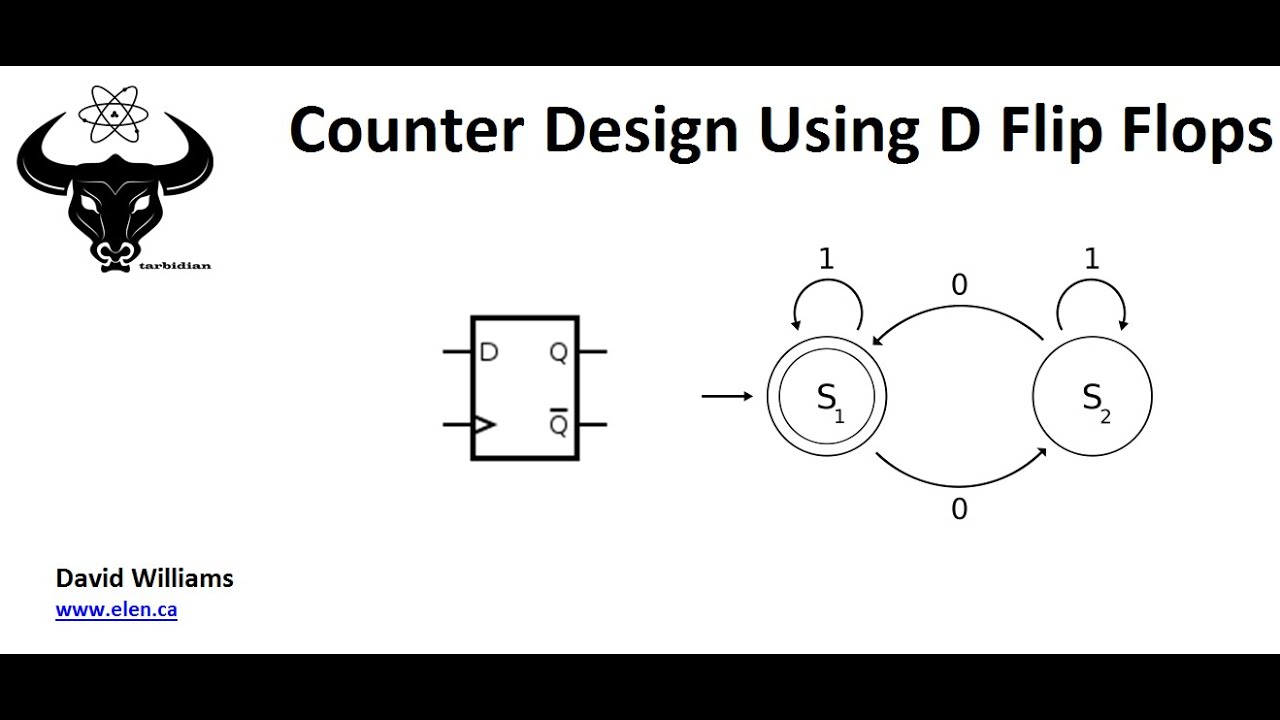

Solution Synchronous Up Down Counter Using Jk Flipflop Studypool A synchronous counter is a type of counter in which all the flip flops are triggered simultaneously by the same clock pulse. the systematic procedure of designing a synchronous counter is explained below. Essentially, a counter consists of cascade connection of a number of flip flops, usually of either the j k type or the d type which may be operated either synchronously or non synchronously. with synchronous operation all the flip flops making up the counter operate at the same instant in time under the control of a clock pulse. The main objective of my channel is to provide free and easy video lectures of different subjects of b.tech. diploma (ece,cse and eee) students and math's and math's olympiad video for my little. Example: 3 bit up counter state diagram 000 001 010 011 from the state diagram we can construct a state transition table (let the variables be a (msb), b and c).

Solution 3 Bit Synchronous Up Down Counter Using Sr Flipflop Studypool The main objective of my channel is to provide free and easy video lectures of different subjects of b.tech. diploma (ece,cse and eee) students and math's and math's olympiad video for my little. Example: 3 bit up counter state diagram 000 001 010 011 from the state diagram we can construct a state transition table (let the variables be a (msb), b and c). We'll design a 3 bit synchronous up counter using d flip flops. this means all flip flops will clock simultaneously, and the counter will increment by one with each clock pulse. This project article provides you to understand how does the up counting operation is performed on the hardware. also, all theoretical calculations, screen shot of the computer simulation and. A synchronous counter is a counter in which all the flip flops are clocked at the same instant. where as in a asynchronous counter, flip flops are clocked at different instant.…. Israel!3 bit synchronous up counter using jk flip flop | design truth table k map timing diagram! audio tracks for some languages were automatically generated. learn more.

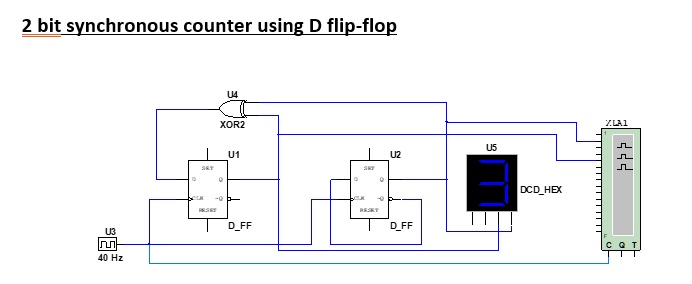

Get Answer 2 Bit Synchronous Counter Using D Flip Flop U3 40 Hz U4 We'll design a 3 bit synchronous up counter using d flip flops. this means all flip flops will clock simultaneously, and the counter will increment by one with each clock pulse. This project article provides you to understand how does the up counting operation is performed on the hardware. also, all theoretical calculations, screen shot of the computer simulation and. A synchronous counter is a counter in which all the flip flops are clocked at the same instant. where as in a asynchronous counter, flip flops are clocked at different instant.…. Israel!3 bit synchronous up counter using jk flip flop | design truth table k map timing diagram! audio tracks for some languages were automatically generated. learn more.

3 Bit Synchronous Counter Using D Flip Flop A synchronous counter is a counter in which all the flip flops are clocked at the same instant. where as in a asynchronous counter, flip flops are clocked at different instant.…. Israel!3 bit synchronous up counter using jk flip flop | design truth table k map timing diagram! audio tracks for some languages were automatically generated. learn more.

Solution Synchronous Up Counter Using D Flipflop Studypool

Comments are closed.