Solution Synchronous Up Down Counter Using Jk Flipflop Studypool

Solution Synchronous Up Down Counter Using Jk Flipflop Studypool Discuss in specific detail how you would deal with the challenges if you were hired for the position, including detailed information and examples of your solutions that would illustrate your total understanding of the environments and their impact on this business. The document outlines the design, simulation, and implementation of a 3 bit synchronous up down counter using jk flip flops, which counts in both ascending and descending order based on a control input.

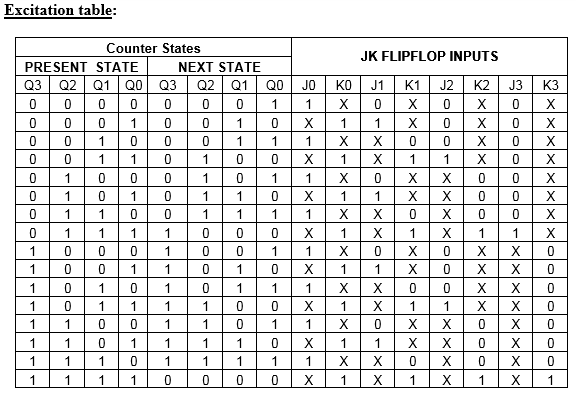

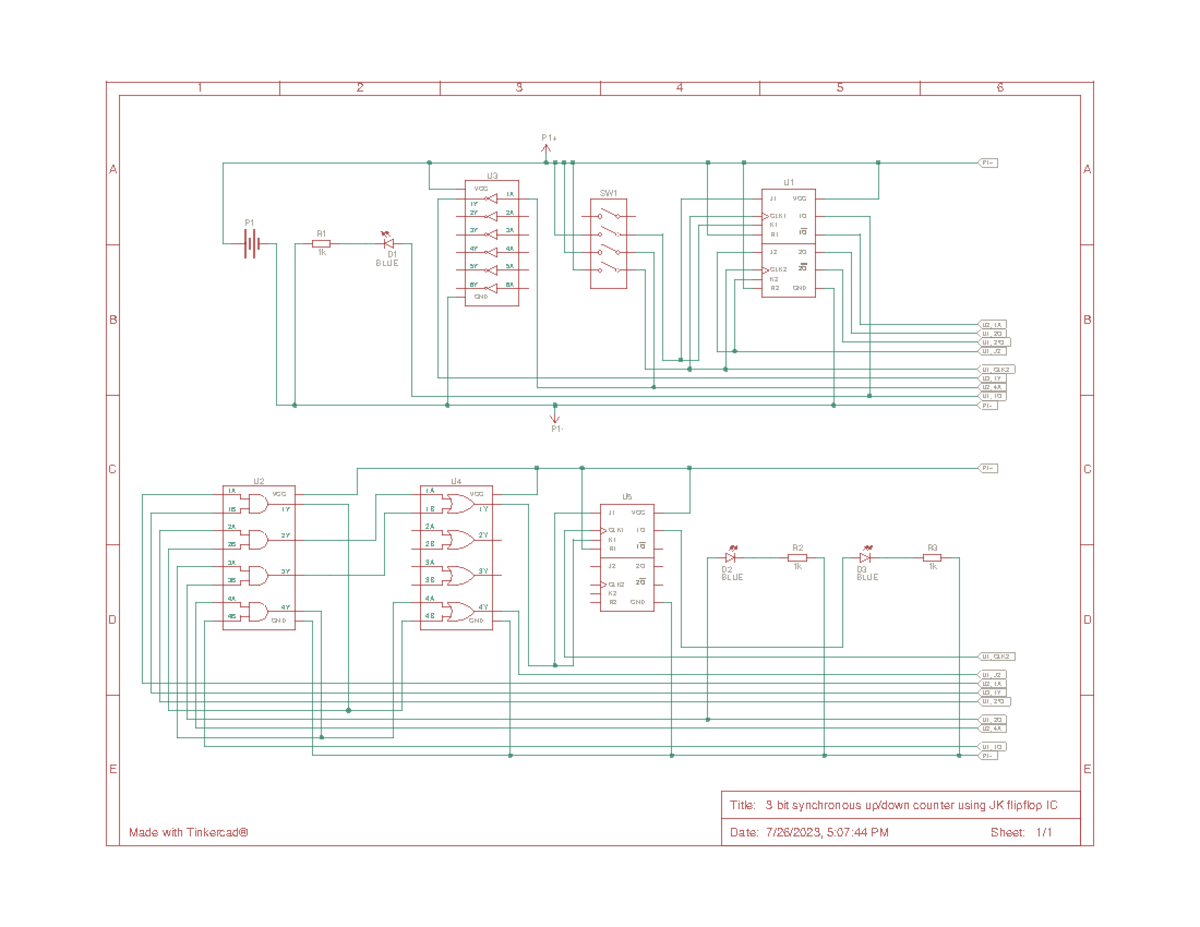

Solution Synchronous Up Down Counter Using Jk Flipflop Studypool To design a synchronous 3 bit up down counter using jk flip flops, we need to follow these steps: 1. understand the operation of jk flip flops. 2. define the states of the counter. 3. create a state transition table for both up and down counting. 4. derive the excitation table for the jk flip flops. 5. The basic ring counter using d flip flops is shown in fig. the realization of this counter using jk ffs. the q output of each stage is connected to the d flip flop connected back to the ring counter. Designed a 3 bit synchronous up down counter using jk flip flops in verilog. wrote the test bench for the same and verified the circuit functionality using some additional combinational logic. 3 bit up down sync counter using jk flipflop tg 3bit ud sync counter using jkff.v at main · tanmay7goyal 3 bit up down sync counter using jk flipflop tg. Aim: to design and implement 3 bit up, down synchronous (ripple) counter using ms jk.

Solution Synchronous Up Down Counter Using Jk Flipflop Studypool Designed a 3 bit synchronous up down counter using jk flip flops in verilog. wrote the test bench for the same and verified the circuit functionality using some additional combinational logic. 3 bit up down sync counter using jk flipflop tg 3bit ud sync counter using jkff.v at main · tanmay7goyal 3 bit up down sync counter using jk flipflop tg. Aim: to design and implement 3 bit up, down synchronous (ripple) counter using ms jk. This experiment focuses on the design, simulation, and implementation of a synchronous counter using jk flip flops. the counter is capable of counting both upwards and downwards based on a control input, demonstrating key principles of sequential logic circuits and synchronous operation. The project involves using altera quartus® ii cad system and proceeding with the following requirements: design and simulation of a four bit up down counter; you will need to use flip flops jk negative edge triggered 74112. At state 1100 (decimal 12), the counter must stop or lock at 1100. this can be achieved by forcing all j and k inputs to zero, or by disabling clock after reaching 1100. Design a 3 bit synchronous up down counter using j k flip flop in this article, we are going to see how to design a three bit synchronous up down counter in detail.

Synchronous Counters Using Jk Flipflop Eees In This experiment focuses on the design, simulation, and implementation of a synchronous counter using jk flip flops. the counter is capable of counting both upwards and downwards based on a control input, demonstrating key principles of sequential logic circuits and synchronous operation. The project involves using altera quartus® ii cad system and proceeding with the following requirements: design and simulation of a four bit up down counter; you will need to use flip flops jk negative edge triggered 74112. At state 1100 (decimal 12), the counter must stop or lock at 1100. this can be achieved by forcing all j and k inputs to zero, or by disabling clock after reaching 1100. Design a 3 bit synchronous up down counter using j k flip flop in this article, we are going to see how to design a three bit synchronous up down counter in detail.

3 Bit Synchronous Up Down Counter Using Jk Flipflop Ic Programming At state 1100 (decimal 12), the counter must stop or lock at 1100. this can be achieved by forcing all j and k inputs to zero, or by disabling clock after reaching 1100. Design a 3 bit synchronous up down counter using j k flip flop in this article, we are going to see how to design a three bit synchronous up down counter in detail.

Comments are closed.