Predictable Accelerator Design With Time Sensitive Affine Types

A Reconfigurable Cnn Based Accelerator Design For Pdf Field This paper proposes a type system that restricts hls to programs that can predictably compile to hardware accelerators. the key idea is to model consumable hardware resources with a time sensitive affine type system that prevents simultaneous uses of the same hardware structure. This paper proposes a type system that restricts hls to programs that can predictably compile to hardware accelerators. the key idea is to model consumable hardware resources with a time sensitive affine type system that prevents simultaneous uses of the same hardware structure.

Predictable Growth Accelerator We extend afine types with time sensitivity to express that repeated uses of the same hardware is safe as long as they are temporally separated. we describe dahlia, a programming language for pre dictable accelerator design. The key idea is to model consumable hardware re sources with a 25 24 time sensitive afine type system that prevents conflicting simultaneous uses of the same hardware structure. This paper proposes a type system that restricts hls to programs that can predictably compile to hardware accelerators. Hls really works!* * when you unroll designs * when unrolling and partitioning are aligned * when partitioning and memory sizes are aligned * when ports times partitioning is a factor of unrolling * when memory accesses are easily analyzable * * * * * when reduction patterns are easily analyzable *.

A Reconfigurable Cnn Based Accelerator Design For Fast And Pdf This paper proposes a type system that restricts hls to programs that can predictably compile to hardware accelerators. Hls really works!* * when you unroll designs * when unrolling and partitioning are aligned * when partitioning and memory sizes are aligned * when ports times partitioning is a factor of unrolling * when memory accesses are easily analyzable * * * * * when reduction patterns are easily analyzable *. Predictable accelerator design with time sensitive affine types this paper proposes a type system that restricts hls to programs that can predictably compile to hardware accelerators. This paper proposes a type system that restricts hls to programs that can predictably compile to hardware accelerators. the key idea is to model consumable hardware resources with a time sensitive affine type system that prevents conflicting simultaneous uses of the same hardware structure. Dahlia is a programming language for designing hardware accelerators. it provides abstractions that guarantee predictable hardware generation after type checking.

A Reconfigurable Cnn Based Accelerator Design For Fast And Energy Predictable accelerator design with time sensitive affine types this paper proposes a type system that restricts hls to programs that can predictably compile to hardware accelerators. This paper proposes a type system that restricts hls to programs that can predictably compile to hardware accelerators. the key idea is to model consumable hardware resources with a time sensitive affine type system that prevents conflicting simultaneous uses of the same hardware structure. Dahlia is a programming language for designing hardware accelerators. it provides abstractions that guarantee predictable hardware generation after type checking.

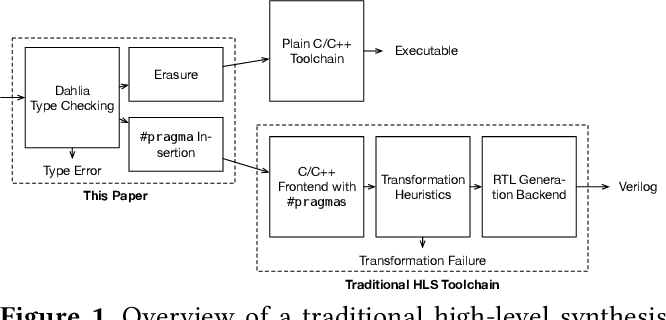

Figure 1 From Predictable Accelerator Design With Time Sensitive Affine Dahlia is a programming language for designing hardware accelerators. it provides abstractions that guarantee predictable hardware generation after type checking.

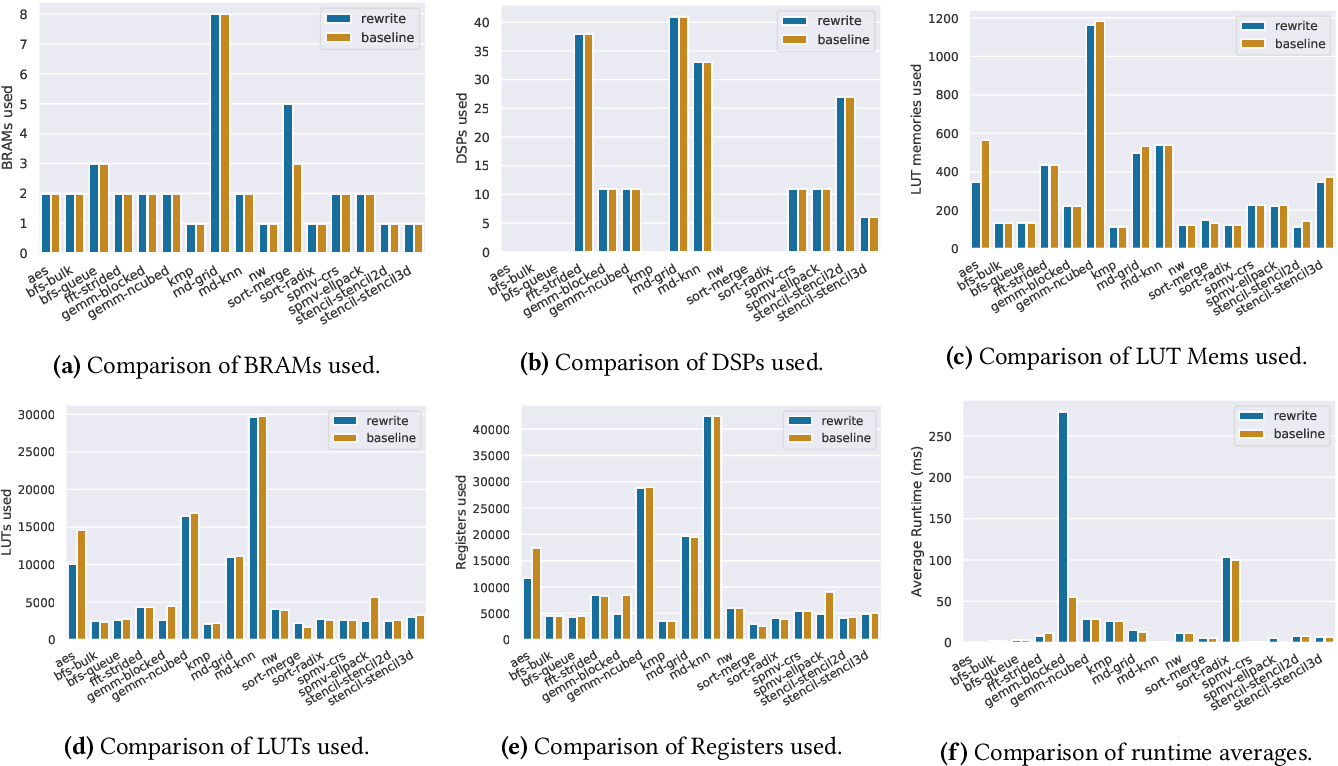

Figure 11 From Predictable Accelerator Design With Time Sensitive

Comments are closed.