Accelerator Design Flow Soc Labs

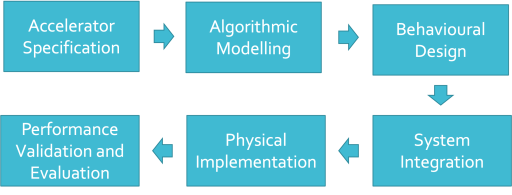

Github Keremsar Soc Design Labs Drawing up a specification for your accelerator is an incredibly important first step of the design flow. it is important to lay out the functionality of your accelerator and to specify important external requirements which may be partially dictated by the system architecture. Early functional and nonfunctional performance analysis to support design decisions. analysis and optimization of hardware software tradeoffs, algorithms, and architectures based on requirements and implementation constraints.

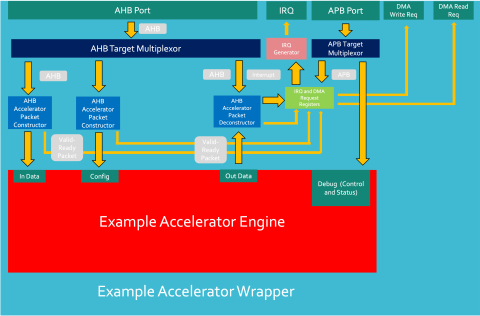

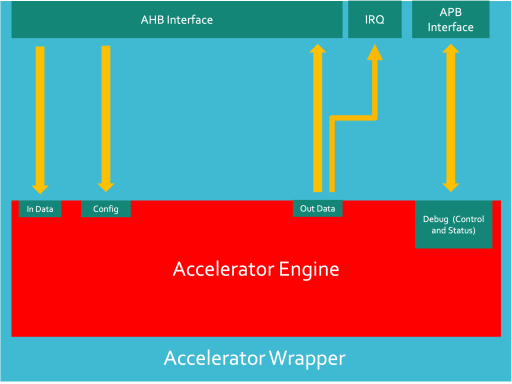

Soc Labs Accelerator Wrapper Soc Labs The platform combines a modular tile based architecture with a variety of application oriented flows for the design and optimization of accelerators. We present a design flow for the seamless hardware and software integration of accelerators into a complete soc and for its evaluation through rapid fpga based prototyping. Cyclone v socs reduce system power, cost, and board size while increasing system performance by integrating discrete processor, fpga, and dsp functions into a single, user customizable arm based (soc). The dataflow of hardware accelerator has a great impact on the performance and energy efficiency. therefore, it is of significant importance to simulate and optimize a dataflow early in the.

Soc Labs Accelerator Wrapper Soc Labs Cyclone v socs reduce system power, cost, and board size while increasing system performance by integrating discrete processor, fpga, and dsp functions into a single, user customizable arm based (soc). The dataflow of hardware accelerator has a great impact on the performance and energy efficiency. therefore, it is of significant importance to simulate and optimize a dataflow early in the. The design flow section explains the steps needed to develop a soc design with tools and other support from our semiconductor education alliance partners and other industry organisations. “h w and s w development concurrently : functionality, timing, physical design, and verification”. The design flow for any project spans the four high level generic stages, each describing the steps that need to be completed when developing a soc design. the example flows section describes specific flow tool implementations showing different ways to implement a flow unique for your project. This repository contains design and verification resources to wrap accelerators with to allow the to plug into the soc labs nanosoc soc infrastructure. subsystem for basic cocotb testing of an axi system. using an arm nic400, dma350 and bp140.

Accelerator Design Flow Soc Labs The design flow section explains the steps needed to develop a soc design with tools and other support from our semiconductor education alliance partners and other industry organisations. “h w and s w development concurrently : functionality, timing, physical design, and verification”. The design flow for any project spans the four high level generic stages, each describing the steps that need to be completed when developing a soc design. the example flows section describes specific flow tool implementations showing different ways to implement a flow unique for your project. This repository contains design and verification resources to wrap accelerators with to allow the to plug into the soc labs nanosoc soc infrastructure. subsystem for basic cocotb testing of an axi system. using an arm nic400, dma350 and bp140.

Accelerator Design Flow Soc Labs The design flow for any project spans the four high level generic stages, each describing the steps that need to be completed when developing a soc design. the example flows section describes specific flow tool implementations showing different ways to implement a flow unique for your project. This repository contains design and verification resources to wrap accelerators with to allow the to plug into the soc labs nanosoc soc infrastructure. subsystem for basic cocotb testing of an axi system. using an arm nic400, dma350 and bp140.

Soc Labs Vlsi System Design

Comments are closed.