Ppt Multi Cycle Cpu Architecture Implementation Execution Steps

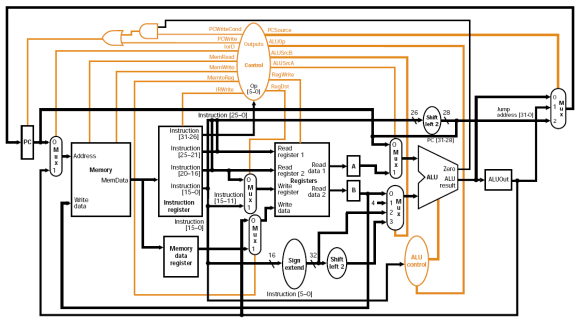

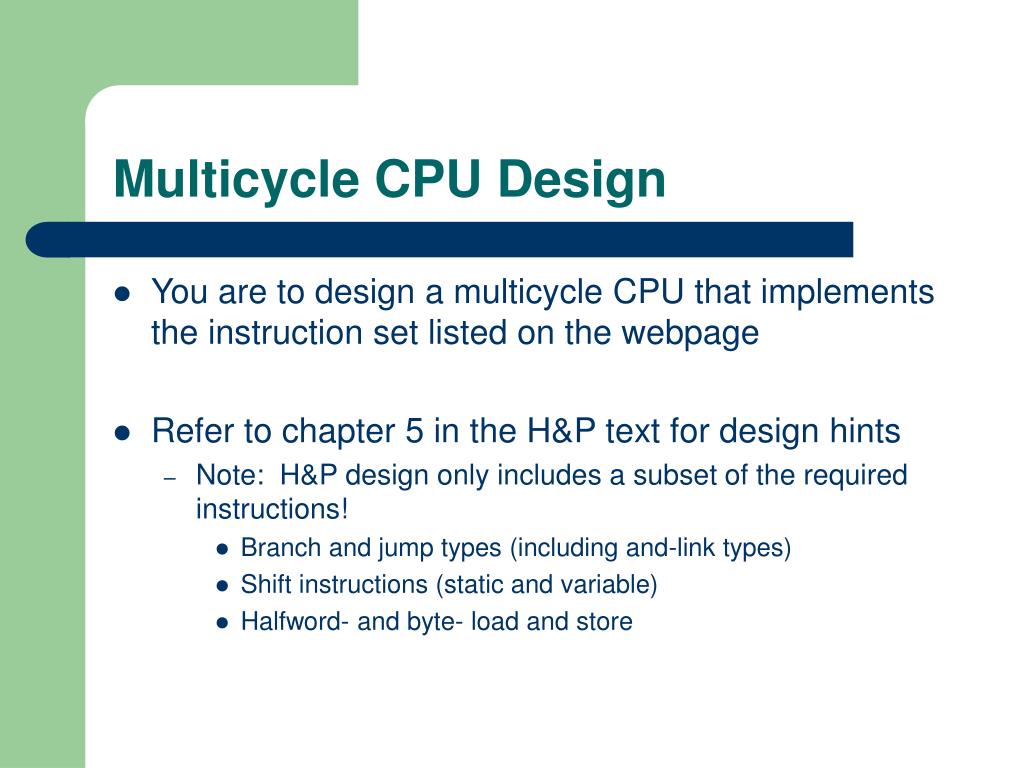

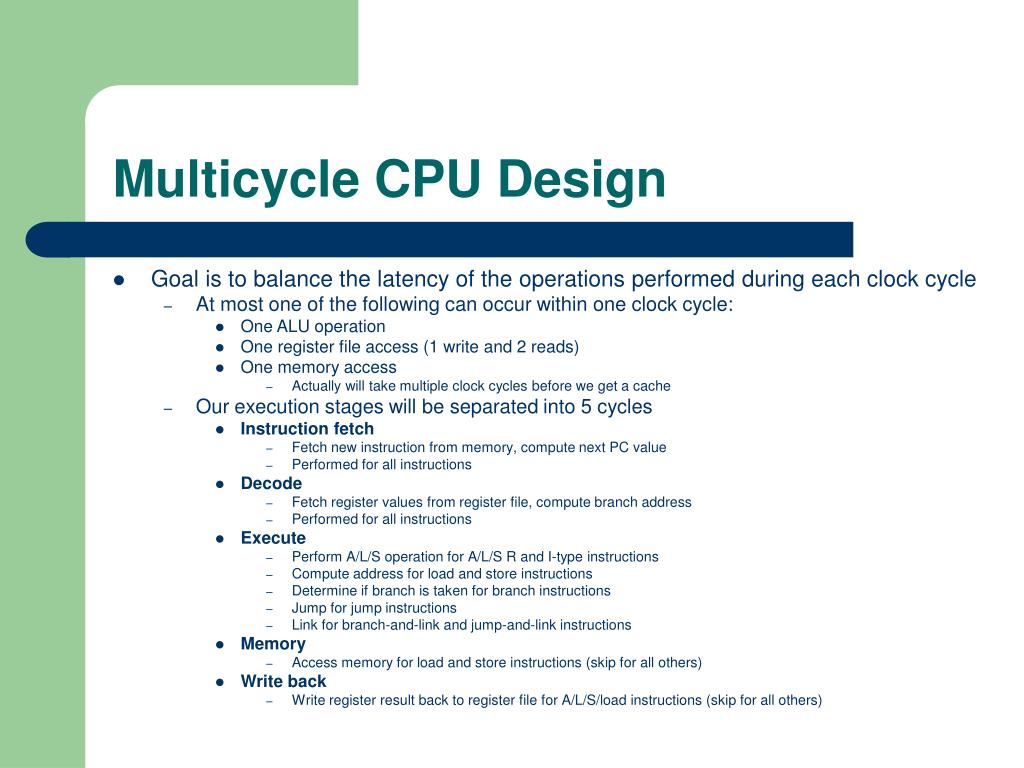

Github Udayakavinda Single Cycle Cpu Implementation Design A Cpu Explore why a multi cycle approach is chosen over single cycle or pipelined designs for cpu hardware, emphasizing hardware reuse and ease of implementation. learn about instruction formats, data flow, and steps in a multi cycle implementation. Instead of executing every instruction in a single, extended clock cycle, multicycle designs divide the instruction execution into several smaller steps, each completed in a shorter clock cycle.

Testing Execution, memory address computation, or branch completion succinctly using rtl 'register transfer language' – a free powerpoint ppt presentation (displayed as an html5 slide show) on powershow id: 221ea3 zdc1z. Breaking execution into clock cycles • we will have five execution steps (not all instructions use all five) – fetch – decode & register fetch – execute – memory access – write back • we will use register transfer language (rtl) to describe these steps cse 141, s2'06 jeff brown. Multi cycle control fsm the finite state control essentially corresponds to the five steps of execution. each state in the finite state machine will take 1 clock cycle. the finite state machine will consist of several parts. For fixed single cycle implementation: clock cycle = 880 ps determined by longest delay (load instruction) for multi cycle implementation: clock cycle = max (200, 150, 180) = 200 ps (maximum delay at any step) average cpi = 0.4×4 0.2×5 0.1×4 0.2×3 0.1×2 = 3.8 speedup = 880 ps (3.8 × 200 ps) = 880 760 = 1.16.

Github H Ssiqueira Cpu Multicycle Implementação De Uma Cpu Multiciclo Multi cycle control fsm the finite state control essentially corresponds to the five steps of execution. each state in the finite state machine will take 1 clock cycle. the finite state machine will consist of several parts. For fixed single cycle implementation: clock cycle = 880 ps determined by longest delay (load instruction) for multi cycle implementation: clock cycle = max (200, 150, 180) = 200 ps (maximum delay at any step) average cpi = 0.4×4 0.2×5 0.1×4 0.2×3 0.1×2 = 3.8 speedup = 880 ps (3.8 × 200 ps) = 880 760 = 1.16. Quick recap various metrics in design of processor the interface & internal structure instruction set architecture assembly instructions instruction encoding outline risc multi cycle execution pipelining reduced instruction set computer (risc) limited no. of instructions fixed length simple to decode easier to implement in hardware prevalent in. Processor: multi cycle datapath & control (based on text: david a. patterson & john l. hennessy, computer organization and design: the hardware software interface, 3rd ed., morgan kaufmann, 2007). Download multicycle implementation lecture slides | cs 5504 and more computer architecture and organization study notes in pdf only on docsity!. Functional units can be shared if used by different instructions single cycle datapath is not efficient in time clock cycle time is determined by the instruction taking the longest time. eg. lw in mips variable clock cycle time is too complicated.

Ppt Coe 1502 Mips Multicycle Cpu Architecture Sequential Logic Quick recap various metrics in design of processor the interface & internal structure instruction set architecture assembly instructions instruction encoding outline risc multi cycle execution pipelining reduced instruction set computer (risc) limited no. of instructions fixed length simple to decode easier to implement in hardware prevalent in. Processor: multi cycle datapath & control (based on text: david a. patterson & john l. hennessy, computer organization and design: the hardware software interface, 3rd ed., morgan kaufmann, 2007). Download multicycle implementation lecture slides | cs 5504 and more computer architecture and organization study notes in pdf only on docsity!. Functional units can be shared if used by different instructions single cycle datapath is not efficient in time clock cycle time is determined by the instruction taking the longest time. eg. lw in mips variable clock cycle time is too complicated.

Ppt Coe 1502 Mips Multicycle Cpu Architecture Sequential Logic Download multicycle implementation lecture slides | cs 5504 and more computer architecture and organization study notes in pdf only on docsity!. Functional units can be shared if used by different instructions single cycle datapath is not efficient in time clock cycle time is determined by the instruction taking the longest time. eg. lw in mips variable clock cycle time is too complicated.

Comments are closed.