Need Part E Please 2 Risc V Single Cycle Data Path Chegg

Need Part E Please 2 Risc V Single Cycle Data Path Chegg Risc v single cycle data path (10pts) consider the complete rv32i datapath above. assuming the following delays (in ps) for the components in the risc v single cycle datapath:. This article continues from the foundational concepts of risc architecture, explaining the datapaths for r type, memory, and i type instructions, alongside control transfer mechanisms.

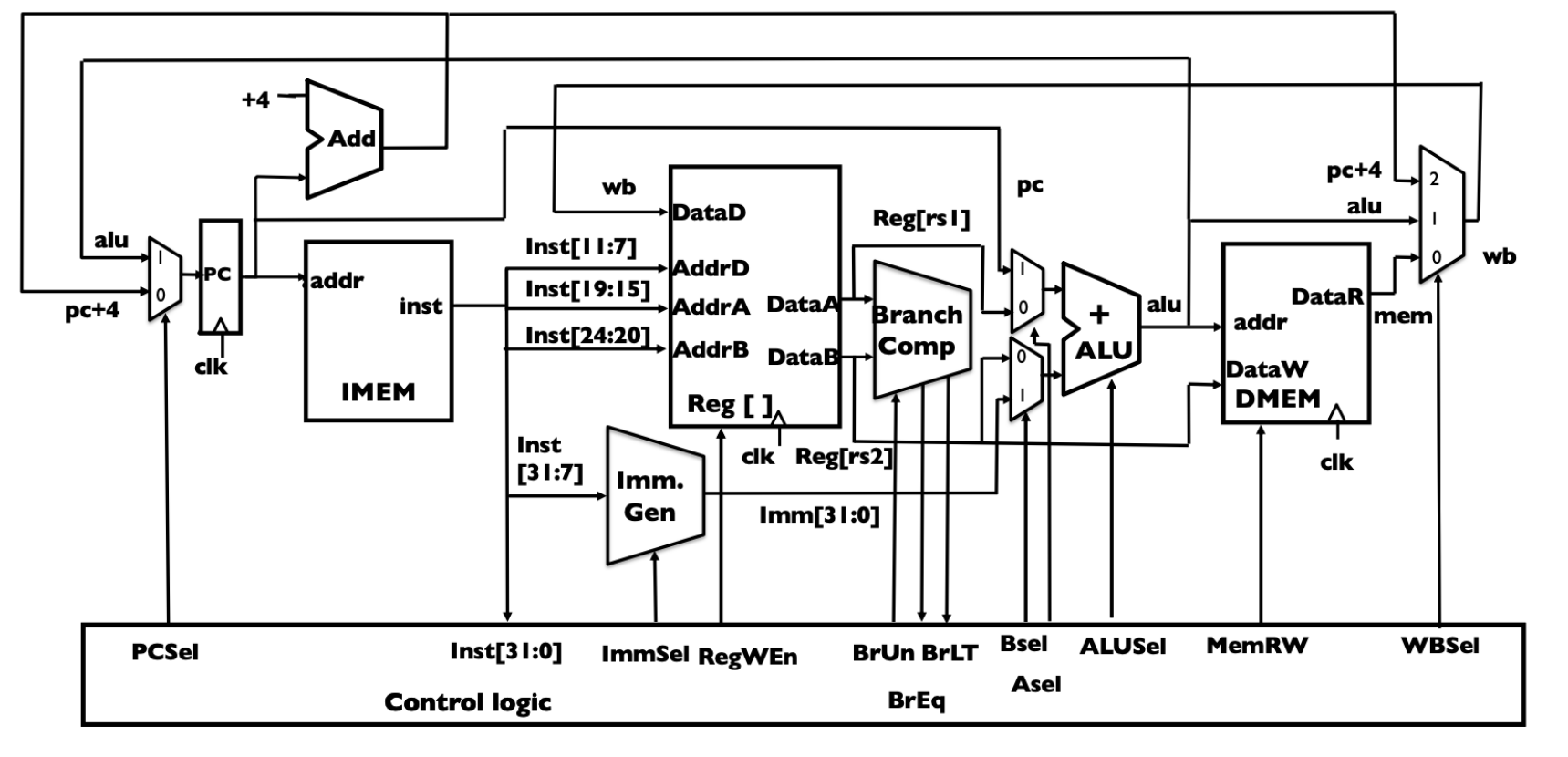

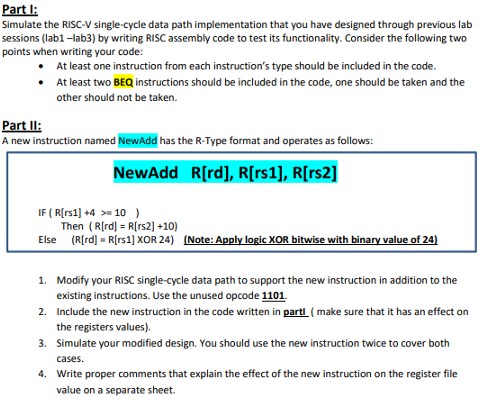

Solved Part 1 Simulate The Risc V Single Cycle Data Path Chegg Receive 20 % off the first month of a new chegg study or chegg study pack monthly subscription. this offer requires activation of a new chegg study or chegg study pack monthly recurring subscription, charged at the monthly rate disclosed at your sign up. There are 2 steps to solve this one. this question asks you to analyze the critical 2. risc v single cycle data path (10pts) consider the complete rv32i datapath above. This document discusses the design of a risc v single cycle datapath, emphasizing the importance of understanding the instruction set architecture (isa) before diving into processor organization. In this repository of risc v, you will get to know the main modules of the mips architecture with their codes, testbench and the design using the verilog language only.

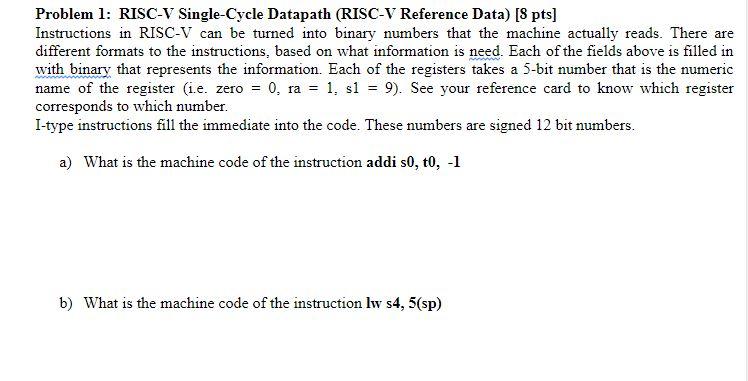

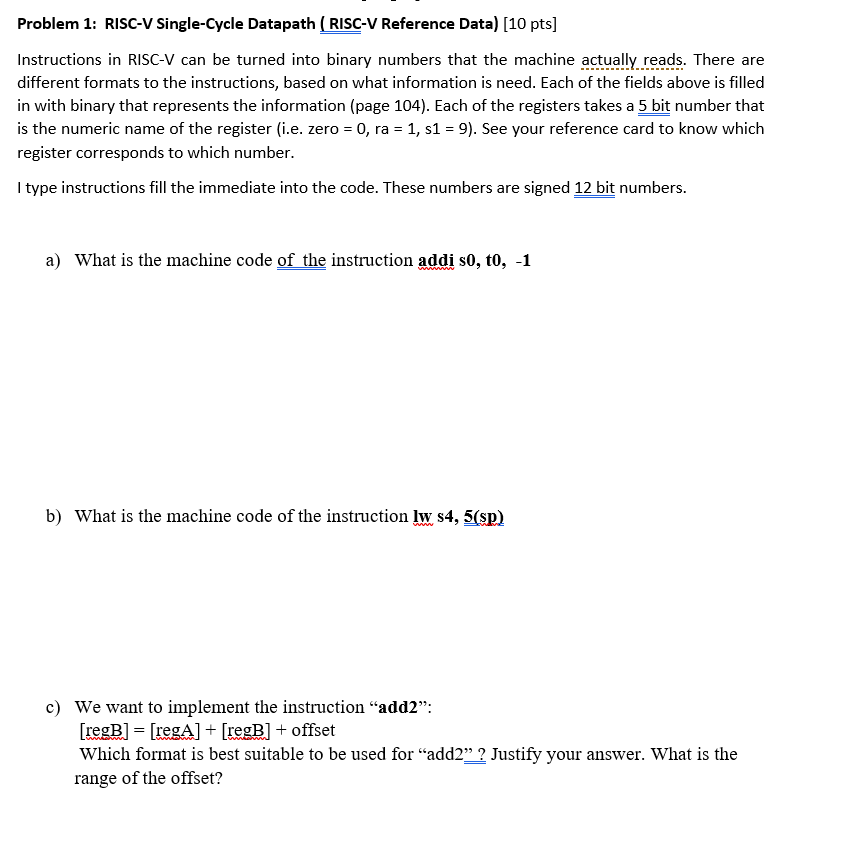

Solved Problem 1 Risc V Single Cycle Datapath Risc V Chegg This document discusses the design of a risc v single cycle datapath, emphasizing the importance of understanding the instruction set architecture (isa) before diving into processor organization. In this repository of risc v, you will get to know the main modules of the mips architecture with their codes, testbench and the design using the verilog language only. Slides for risc v single cycle implementalon are adapted from computer science 152: computer architecture and engineering, spring 2016 by dr. george michelogiannakis from uc berkeley. Figure 1 shows the datapath of a risc v single cycle processor. the instruction execution starts by using the program counter to supply the instruction address to the instruction memory. This time, we are going to learn how to design a single cycle riscv processor using the scala programming language. throughout the process, we need to complete the implementation of the code for each stage. Skills you will gain: trace the complete data flow for different risc v instruction types (r, i, j, s, b). interpret control signals to explain why the datapath behaves differently for each instruction. analyze the performance limitations and structural trade offs inherent in a single cycle processor design. propose and justify conceptual.

Problem 1 Risc V Single Cycle Datapath Risc V Chegg Slides for risc v single cycle implementalon are adapted from computer science 152: computer architecture and engineering, spring 2016 by dr. george michelogiannakis from uc berkeley. Figure 1 shows the datapath of a risc v single cycle processor. the instruction execution starts by using the program counter to supply the instruction address to the instruction memory. This time, we are going to learn how to design a single cycle riscv processor using the scala programming language. throughout the process, we need to complete the implementation of the code for each stage. Skills you will gain: trace the complete data flow for different risc v instruction types (r, i, j, s, b). interpret control signals to explain why the datapath behaves differently for each instruction. analyze the performance limitations and structural trade offs inherent in a single cycle processor design. propose and justify conceptual.

Github Mkrekker Single Cycle Risc V This time, we are going to learn how to design a single cycle riscv processor using the scala programming language. throughout the process, we need to complete the implementation of the code for each stage. Skills you will gain: trace the complete data flow for different risc v instruction types (r, i, j, s, b). interpret control signals to explain why the datapath behaves differently for each instruction. analyze the performance limitations and structural trade offs inherent in a single cycle processor design. propose and justify conceptual.

Comments are closed.