Risc V Single Cycle Datapath

Risc V Datapath Summary Pdf Computer Architecture Office Equipment In this article, we will focus on understanding the rv32i single cycle datapath (scdp) and its core components. Universal datapath − capable of executing all risc v instructions in one cycle each − not all units (hardware) used by all instructions 5 phases of execution − if (instruction fetch), id (instruction decode), ex (execute), mem (memory), wb (write back) − not all instructions are active in all phases (except for loads!).

Github Mkrekker Single Cycle Risc V Fetch, decode and execute each instruction in one clock cycle – single cycle design no datapath resource can be used more than once per instruction, so some must be duplicated (e.g., why we have a separate instruction memory and data memory). In this repository of risc v, you will get to know the main modules of the mips architecture with their codes, testbench and the design using the verilog language only. This document discusses the design of a risc v single cycle datapath, emphasizing the importance of understanding the instruction set architecture (isa) before diving into processor organization. Design the datapath (2 3) the single cycle processor all stages of one rv32i instruction execute within the same clock cycle.

Github Basmagfawzy Single Cycle Risc V Processor This document discusses the design of a risc v single cycle datapath, emphasizing the importance of understanding the instruction set architecture (isa) before diving into processor organization. Design the datapath (2 3) the single cycle processor all stages of one rv32i instruction execute within the same clock cycle. Control is the sequential logic that reconfigures the datapath to allow the “data” to flow properly through the hardware components. This article continues from the foundational concepts of risc architecture, explaining the datapaths for r type, memory, and i type instructions, alongside control transfer mechanisms. Slides for risc v single cycle implementalon are adapted from computer science 152: computer architecture and engineering, spring 2016 by dr. george michelogiannakis from uc berkeley. This paper outlines the design of a low process control system for embedded systems applications, utilizing a risc v processor. the design incorporates functio.

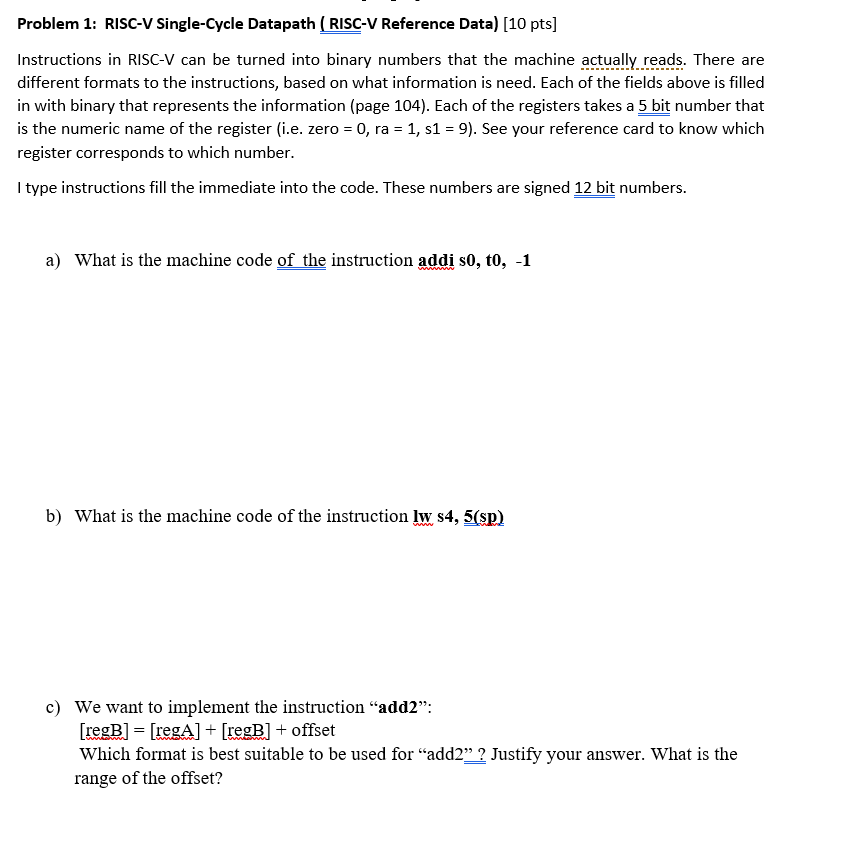

Problem 1 Risc V Single Cycle Datapath Risc V Chegg Control is the sequential logic that reconfigures the datapath to allow the “data” to flow properly through the hardware components. This article continues from the foundational concepts of risc architecture, explaining the datapaths for r type, memory, and i type instructions, alongside control transfer mechanisms. Slides for risc v single cycle implementalon are adapted from computer science 152: computer architecture and engineering, spring 2016 by dr. george michelogiannakis from uc berkeley. This paper outlines the design of a low process control system for embedded systems applications, utilizing a risc v processor. the design incorporates functio.

Github Nihargowdas Single Cycle Risc V Processor Slides for risc v single cycle implementalon are adapted from computer science 152: computer architecture and engineering, spring 2016 by dr. george michelogiannakis from uc berkeley. This paper outlines the design of a low process control system for embedded systems applications, utilizing a risc v processor. the design incorporates functio.

Github Nihargowdas Single Cycle Risc V Processor

Comments are closed.