Multi Level Logic Synthesis

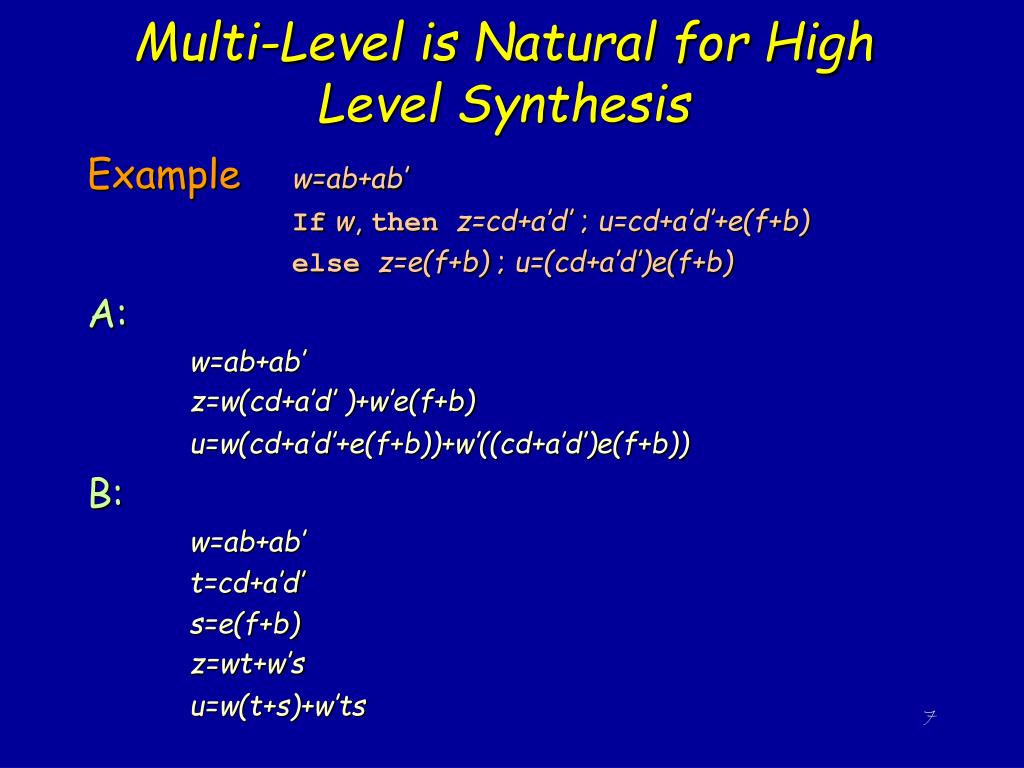

Solved 2 Multi Level Network Logic Synthesis A Convert Chegg In chapter 4, we discussed techniques for obtaining minimal two level and–or or or–and realizations. in the present chapter we generalize the discussion to the synthesis of multi level realizations, i.e., those that contain more than two levels of logic gates. Multi level logic networks often require fewer gates and fewer connections than two level logic networks. on the other hand, designs of multi level logic net works are far more complex than those of two level logic networks.

Ppt Multi Level Logic Synthesis Introduction Powerpoint Presentation Pdf | a survey of logic synthesis techniques for multilevel combinational logic is presented. Factored forms are useful in estimating area and delay in a multi level synthesis and optimization system. in many design styles (e.g. complex gate cmos design) the implementation of a function corresponds directly to its factored form. Logic synthesis (automatic factoring) combinational optimization 2 level multi level sequential optimization. A survey of logic synthesis techniques for multilevel combinational logic is presented. the goal is to provide more in depth background and perspective for people interested in pursuing or assessing some of the topics in this emerging field.

Ppt Multi Level Logic Synthesis Introduction Powerpoint Presentation Logic synthesis (automatic factoring) combinational optimization 2 level multi level sequential optimization. A survey of logic synthesis techniques for multilevel combinational logic is presented. the goal is to provide more in depth background and perspective for people interested in pursuing or assessing some of the topics in this emerging field. Approximate logic synthesis (als), in particular, treats two level and multilevel topologies of combinational blocks in the development of digital ic design. Digital ic construction can be done at two and multiple levels (three or more) of logic depth. two level (2l) circuit topology comprises logic operations divided into two lay ers. Multilevel logic synthesis proceedings of the ieee. title. multilevel logic synthesis proceedings of the ieee . author. ieee . created date. 2 25 1998 1:40:48 am . Factored forms are useful in estimating area and delay in a multi level synthesis and optimization system, because: in many design styles (e.g. complex gate cmos design) the implementation of a function corresponds directly to its factored form.

Comments are closed.