Ppt Engg3190 Logic Synthesis %ef%be%83 %e7%ab%84%ef%bd%ac%ef%be%85%e6%ba%baulti Level Logic%ef%be%83 %e7%ab%84%ef%bd%ac Part Ii

Ppt Engg3190 Logic Synthesis テ 竄ャナ溺ulti Level Logicテ 竄ャ Part Ii Course objectives • this is an introductory course in logic synthesis for computer engineers. • achieves the following goals: • teaches you the fundamentalconcepts of logic synthesis. • teaches you the way in which electronic design automation systems are designed today. Presentation on theme: "engg3190 logic synthesis “multi level logic” (part i) winter 2014 s. areibi school of engineering university of guelph."— presentation transcript:.

Ppt Engg3190 Logic Synthesis Two Level Logic Synthesis Heuristics Functions • there can be different representations for a boolean function • usually want simplest • fewest gates or using particular types of gates • we can use identities to reduce complexity of boolean expressions. engg3190 logic synthesis. • the circuit above can have between 3 8 logic gates per level • with multi level logic synthesis we can control the number of levels we seek thus the speed of the circuit. Download presentation by click this link. while downloading, if for some reason you are not able to download a presentation, the publisher may have deleted the file from their server. • we are free to treat the x or ‘d’ as a ‘0’ or a ‘1’ • what is different in multi level optimization? if x, b, y are primary inputs then we cannot say anything yet!.

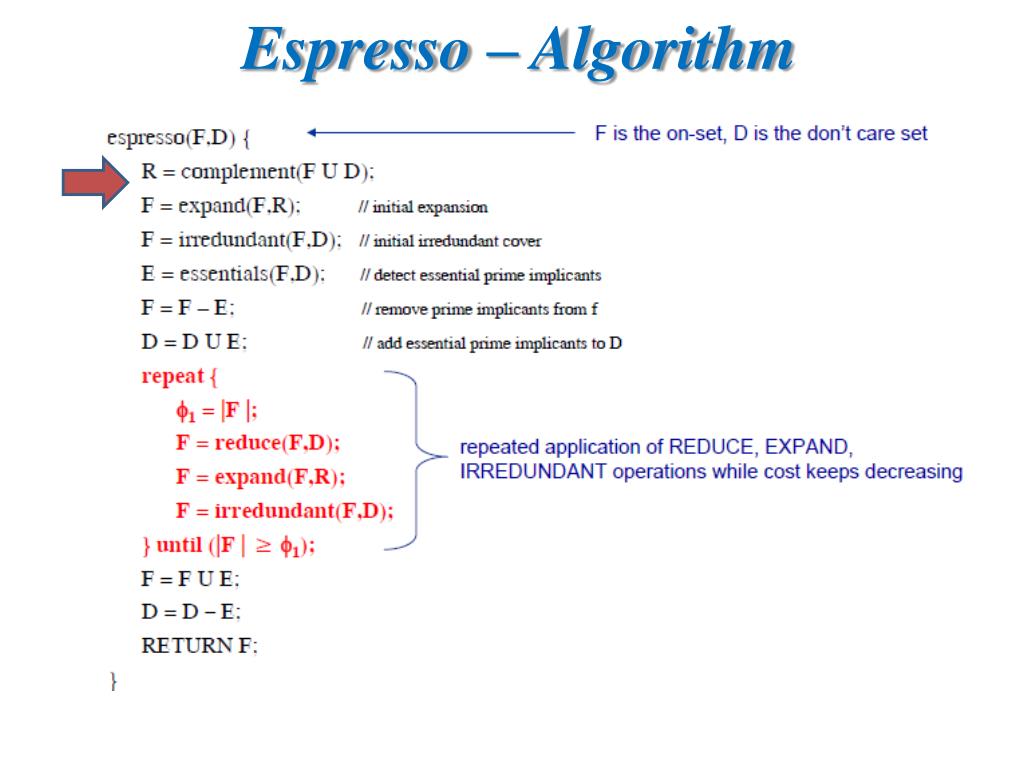

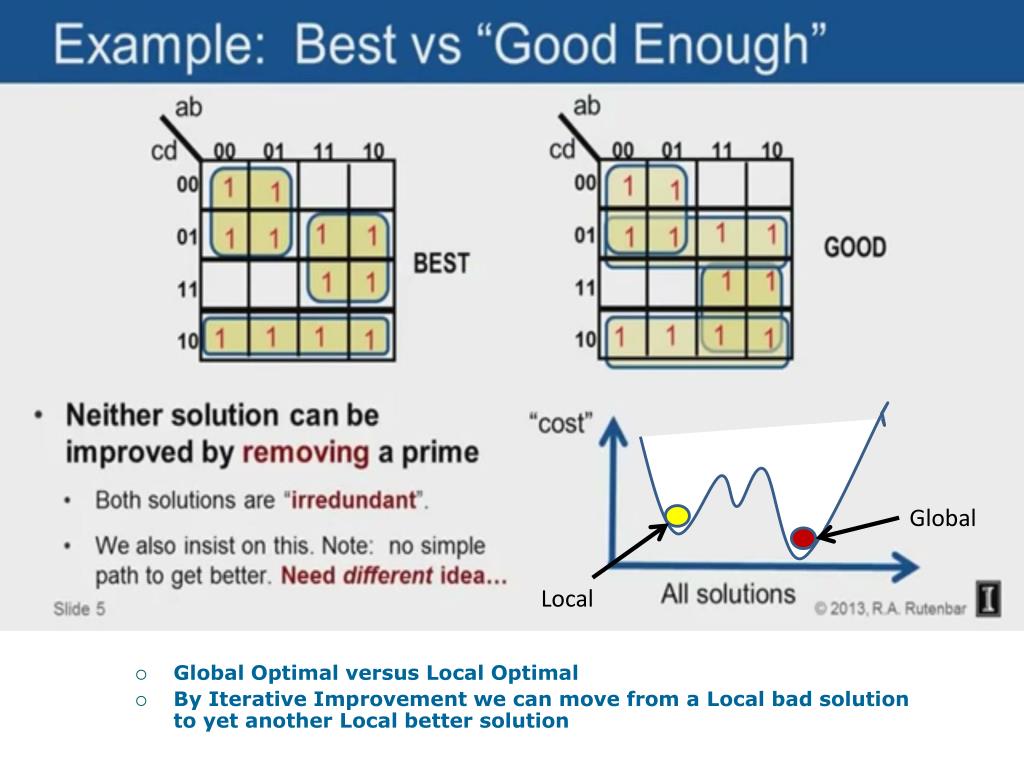

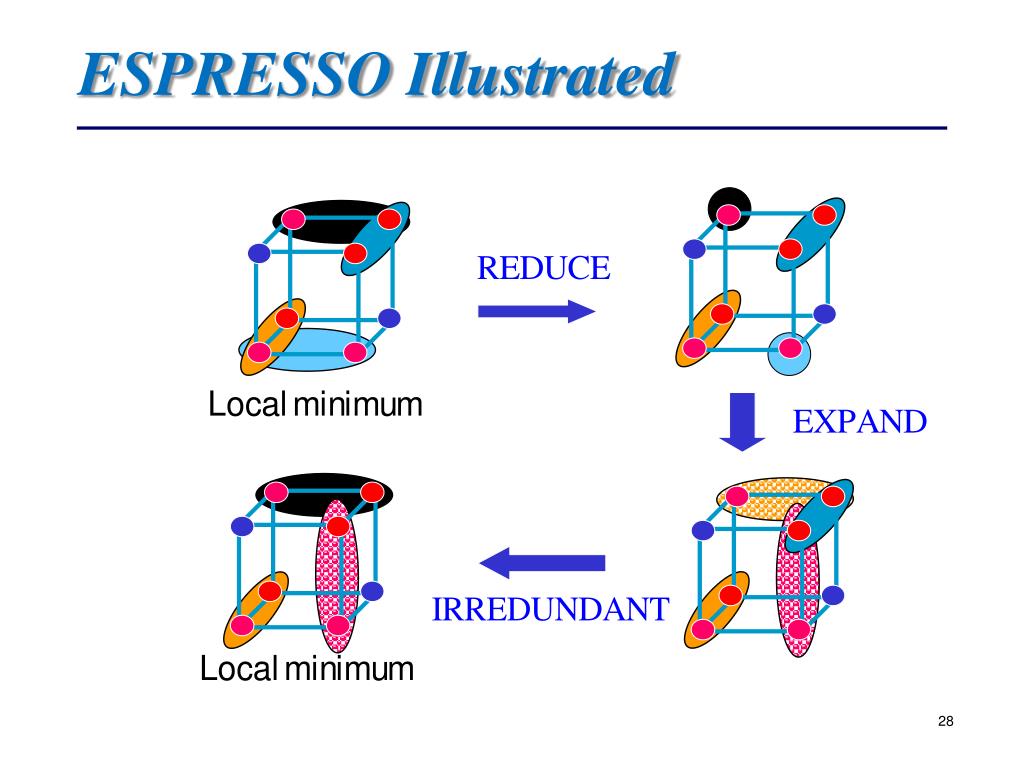

Ppt Engg3190 Logic Synthesis Two Level Logic Synthesis Heuristics Download presentation by click this link. while downloading, if for some reason you are not able to download a presentation, the publisher may have deleted the file from their server. • we are free to treat the x or ‘d’ as a ‘0’ or a ‘1’ • what is different in multi level optimization? if x, b, y are primary inputs then we cannot say anything yet!. Engg3190 logic synthesis “two level logic synthesis: heuristics (espresso)” (part ii). winter 2014 s. areibi school of engineering university of guelph. outline. optimality heuristics espresso expand, reduce, irredundant steps input format comparison: qm vs. espresso. • logic transformations (recall multi level synthesis transformations!!) • state transition diagrams can be: • transformed into synchronous logic networks by state encoding. Presentation on theme: "engg3190 logic synthesis “boolean satisfiability” winter 2014 s. areibi school of engineering university of guelph."— presentation transcript:. This course is an introductory course in logic synthesis. the main goals of the course are (1) to teach students the fundamental concepts of logic synthesis and (2) to illustrate clearly the way in which electronic design automation systems are designed today.

Ppt Engg3190 Logic Synthesis Two Level Logic Synthesis Heuristics Engg3190 logic synthesis “two level logic synthesis: heuristics (espresso)” (part ii). winter 2014 s. areibi school of engineering university of guelph. outline. optimality heuristics espresso expand, reduce, irredundant steps input format comparison: qm vs. espresso. • logic transformations (recall multi level synthesis transformations!!) • state transition diagrams can be: • transformed into synchronous logic networks by state encoding. Presentation on theme: "engg3190 logic synthesis “boolean satisfiability” winter 2014 s. areibi school of engineering university of guelph."— presentation transcript:. This course is an introductory course in logic synthesis. the main goals of the course are (1) to teach students the fundamental concepts of logic synthesis and (2) to illustrate clearly the way in which electronic design automation systems are designed today.

Ppt Engg3190 Logic Synthesis Two Level Logic Synthesis Heuristics Presentation on theme: "engg3190 logic synthesis “boolean satisfiability” winter 2014 s. areibi school of engineering university of guelph."— presentation transcript:. This course is an introductory course in logic synthesis. the main goals of the course are (1) to teach students the fundamental concepts of logic synthesis and (2) to illustrate clearly the way in which electronic design automation systems are designed today.

Comments are closed.