Lecture 34 Multi Level Logic Synthesis

Lecture 34 Pdf Video lecture series from iit professors :digital hardware design by prof. m. balakrishnan. Lecture 34 multi level logic synthesis tutorial of digital hardware design course by prof m.balakrishnan of online tutorials. you can download the course for free !.

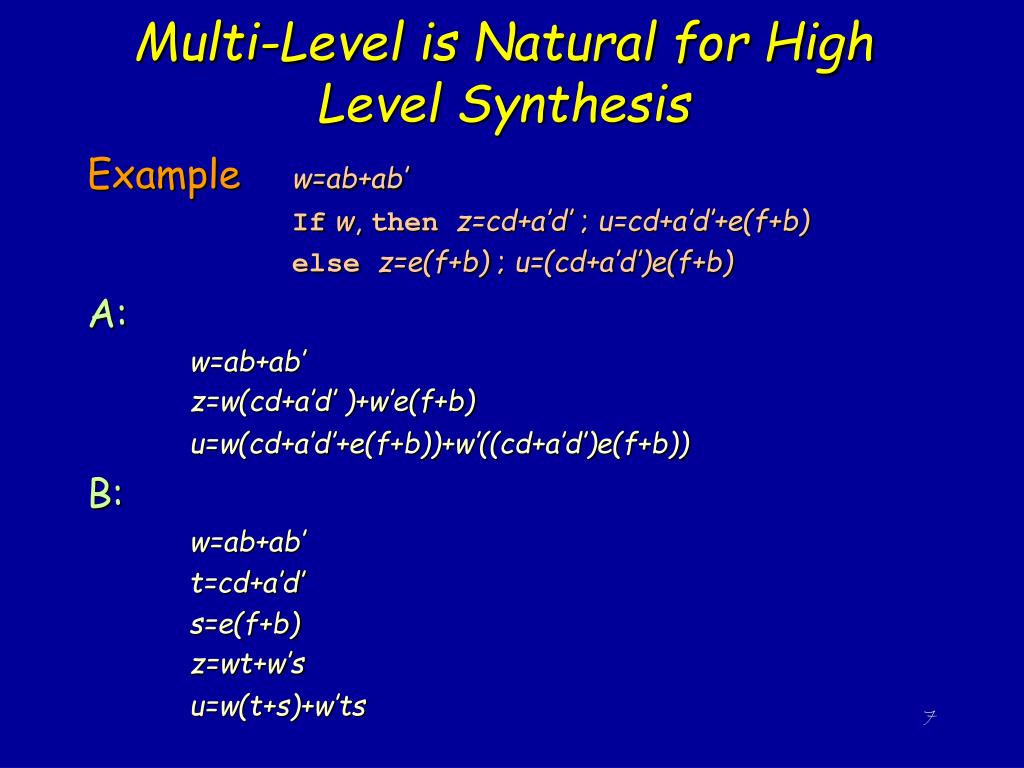

Ppt Multi Level Logic Synthesis Introduction Powerpoint Presentation Example of optimization – node elimination example of example of optimization – 2 level minimization. R.k. brayton, r. rudell, a. sangiovanni vincentelli, a.r. wang, “mis: a multiple level logic optimization system,” ieee transactions on cad of ics, vol. cad 6, no. 6, november 1987, pp. 1062 1081. Chapter 1 representations for boolean functions click to view details chapter 2 two level logic minimization click to view details chapter 3 multi level logic minimization click to view details. Many heuristics use clever ordering of the cubes, and then operate on each cube in some ranked order. mostly doing bit level pcn operations on the cube lists. many of the rest of the operations.

Ppt Multi Level Logic Synthesis Introduction Powerpoint Presentation Chapter 1 representations for boolean functions click to view details chapter 2 two level logic minimization click to view details chapter 3 multi level logic minimization click to view details. Many heuristics use clever ordering of the cubes, and then operate on each cube in some ranked order. mostly doing bit level pcn operations on the cube lists. many of the rest of the operations. Content: introduction to computer aided synthesis and optimization. hardware modeling. We will briefly describe the quine mccluskey method which was the first algorithmic method proposed for two level minimization and which follows the two steps outlined above. In chapter 4, we discussed techniques for obtaining minimal two level and–or or or–and realizations. in the present chapter we generalize the discussion to the synthesis of multi level realizations, i.e., those that contain more than two levels of logic gates. Multi level logic networks often require fewer gates and fewer connections than two level logic networks. on the other hand, designs of multi level logic net works are far more complex than those of two level logic networks.

Comments are closed.