Gals System Design Side Channel Attack Secure Cryptographic Accelerators

Gals System Design Side Channel Attack Secure Cryptographic Accelerators By combining this architecture with several well known countermeasures against side channel attacks, the security of the aes implementation has been improved considerably. this work represents the first application of gals to improve the side channel security of a cryptographic system. This work represents the first application of gals to improve the sidechannel security of a cryptographic system. a mature gals design flow, which is mainly based on industry standard electronic design automation tools, has been used to fabricate the circuit.

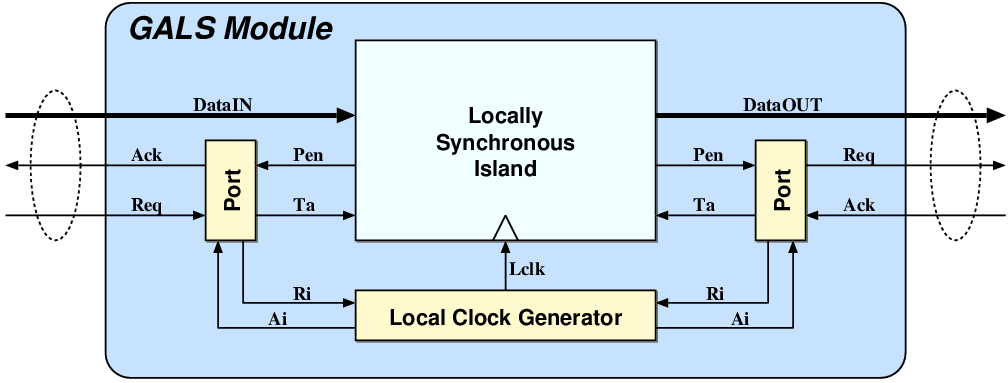

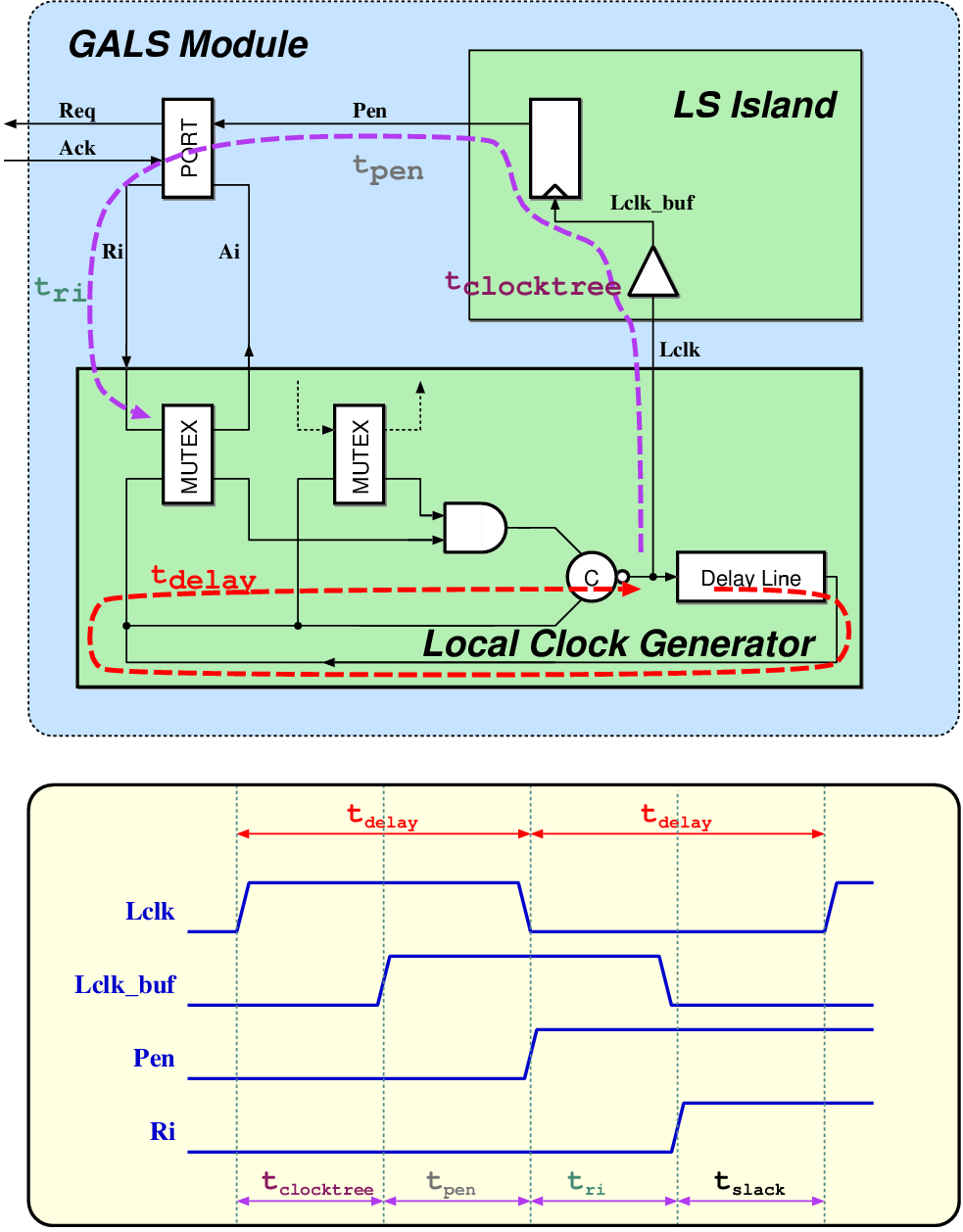

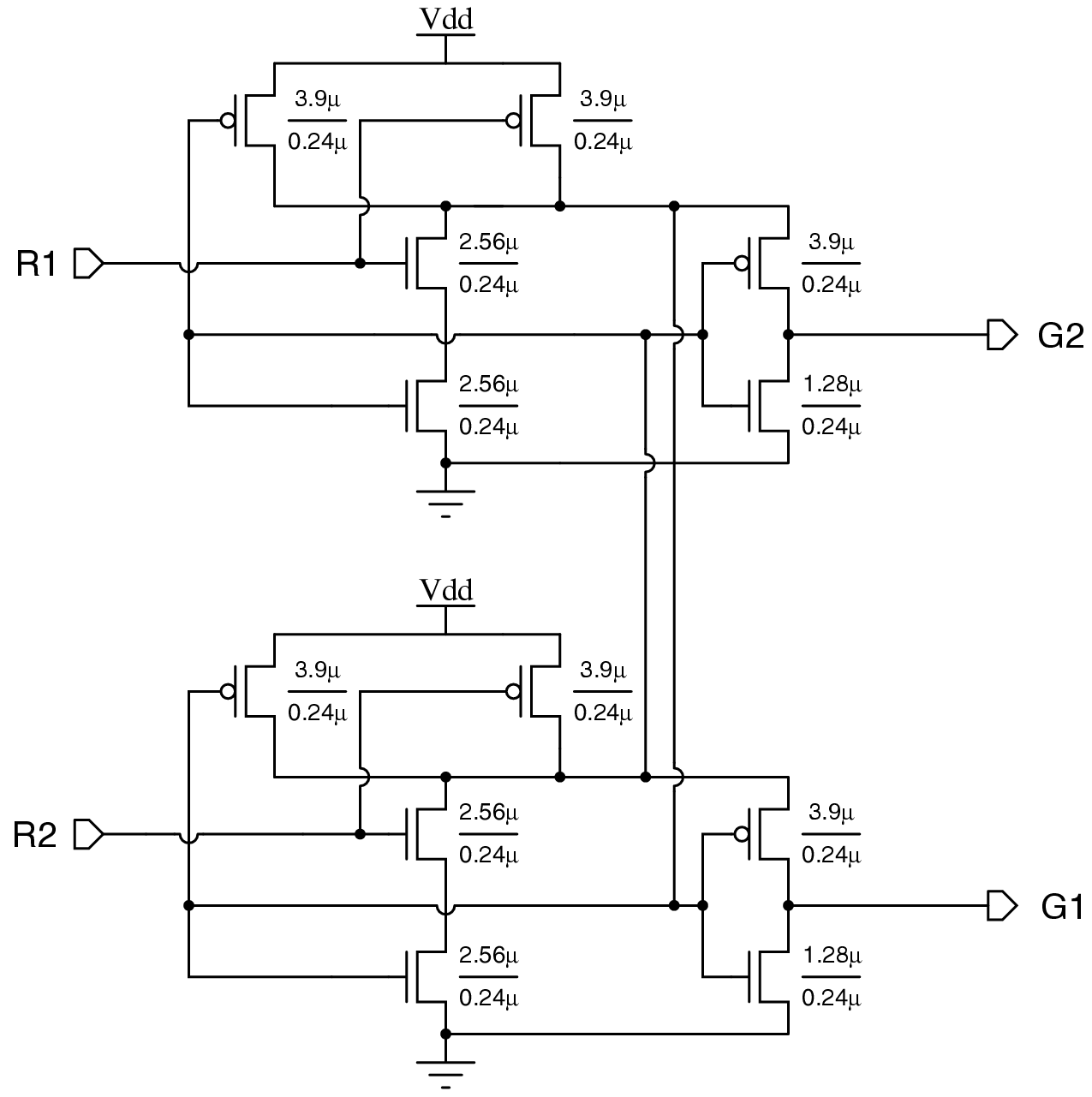

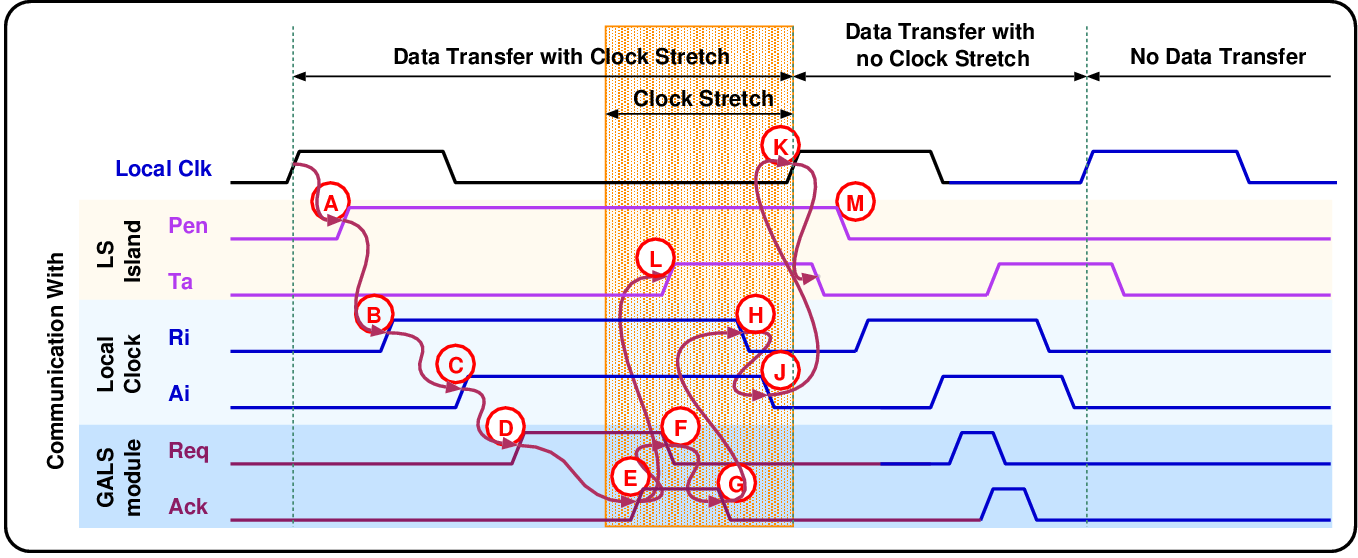

Gals System Design Side Channel Attack Secure Cryptographic Accelerators This presentation will focus on a comparative overview of available alternatives to achieve sub gate resolution at high oscillation frequencies and the viability of the gals approach, demonstrated by the implementation of a safer sk128 crypto system on silicon. In this work, an ecc processor based on the globally asynchronous locally synchronous (gals) design is presented. attention has been paid on the resistances of gals design against side channel attacks (scas). The design presented in chapter 4 is the first application of gals in a cryptographic system and uses several features of gals design to improve side channel security. Gals design methodology allows a very large system to be partition into smaller modules, each of which can be optimized independently. at the top level, the designer only has to realize the interconnections between gals modules which have minor or no timing constraints set on them6.

Gals System Design Side Channel Attack Secure Cryptographic Accelerators The design presented in chapter 4 is the first application of gals in a cryptographic system and uses several features of gals design to improve side channel security. Gals design methodology allows a very large system to be partition into smaller modules, each of which can be optimized independently. at the top level, the designer only has to realize the interconnections between gals modules which have minor or no timing constraints set on them6. This work represents the first application of gals to improve the side channel security of a cryptographic system. a mature gals design flow, which is mainly based on industry standard electronic design automation tools, has been used to fabricate the circuit. Publisher eth subject cryptography (information theory); schaltkreisentwurf (mikroelektronik); kryptographie (informationstheorie); input output datenkommunikation (hardware); circuit design (microelectronics); input output data communications (hardware) organisational unit 03228 fichtner, wolfgang more show all metadata . The proposed hybrid cryptographic framework is designed to address a range of side channel attacks (sca) and cryptanalysis based threats.

Gals System Design Side Channel Attack Secure Cryptographic Accelerators This work represents the first application of gals to improve the side channel security of a cryptographic system. a mature gals design flow, which is mainly based on industry standard electronic design automation tools, has been used to fabricate the circuit. Publisher eth subject cryptography (information theory); schaltkreisentwurf (mikroelektronik); kryptographie (informationstheorie); input output datenkommunikation (hardware); circuit design (microelectronics); input output data communications (hardware) organisational unit 03228 fichtner, wolfgang more show all metadata . The proposed hybrid cryptographic framework is designed to address a range of side channel attacks (sca) and cryptanalysis based threats.

Gals System Design Side Channel Attack Secure Cryptographic Accelerators The proposed hybrid cryptographic framework is designed to address a range of side channel attacks (sca) and cryptanalysis based threats.

Gals System Design Side Channel Attack Secure Cryptographic Accelerators

Comments are closed.