Domain Specific Accelerators Will Drive Vector Processing On Risc V

Risc V2 A Scalable Risc V Vector Process Pdf In risc v, the maturing standard vector extension augmented with specialized custom instructions is an ideal companion to the accelerator, and this adoption has become apparent in the past 18 months as domain specific acceleration (dsa) solutions converge onto risc v platforms. As the risc v architecture became more mature and soc designers became familiar with the isa, it found adoption in real time applications that demanded high performance: in particular, serving as a front end to highly specialized acceleration engines for applications such as artificial intelligence.

Domain Specific Accelerators Will Drive Vector Processing On Risc V Becoming a member of risc v international allows companies and individuals to actively influence the development of an open, royalty free instruction set architecture, driving innovation in custom processor designs. This paper provides a comprehensive review of the latest research on risc v, with a focus on its vector extensions, custom instruction set optimizations, and the design and implementation of. Building on recent access to open source hardware, we explore the software hardware codesign process of integrating and optimizing the end to end dataflow of deep learning accelerator into a risc v system on chip. Domain specific accelerators (dsa) shine on narrow kernels but go dark elsewhere; vectors stay fully programmable, giving cryptography, media, and high performance computing (hpc) workloads high throughput and agility in one engine.

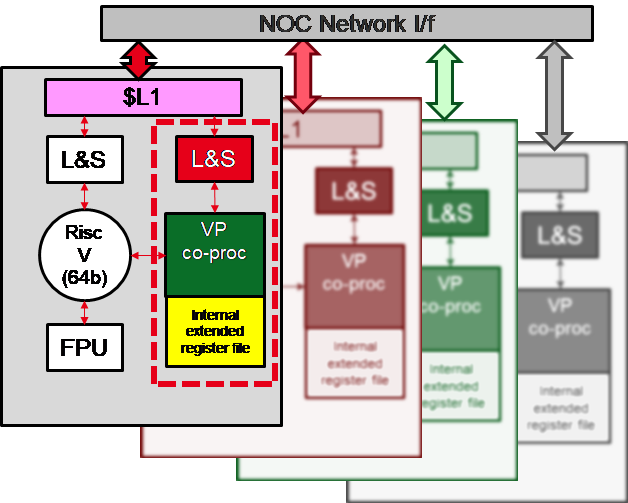

Domain Specific Accelerators Will Drive Vector Processing On Risc V Building on recent access to open source hardware, we explore the software hardware codesign process of integrating and optimizing the end to end dataflow of deep learning accelerator into a risc v system on chip. Domain specific accelerators (dsa) shine on narrow kernels but go dark elsewhere; vectors stay fully programmable, giving cryptography, media, and high performance computing (hpc) workloads high throughput and agility in one engine. In risc v, the maturing standard vector extension augmented with specialized custom instructions is an ideal companion to the accelerator, and this adoption has become apparent in the past 18 months as domain specific acceleration (dsa) solutions converge onto risc v platforms. The availability of risc v processors with vector extension enabled specialized accelerators to process the layers in between inner loops of the kernel for applications such as artificial intelligence (ai), augmented reality virtual reality (ar vr), and computer vision. Developing processor ip combining risc v defined vector extensions (rvv) with custom dsp instructions promises attractive benefits for low power embedded applications requiring signal processing capabilities. Risc v based edge platforms often combine a control processor (with or without a vector extension) and one or more domain accelerators attached via a memory mapped interconnect.

Energy Efficient Risc V Based Vector Processor For Cache Aware In risc v, the maturing standard vector extension augmented with specialized custom instructions is an ideal companion to the accelerator, and this adoption has become apparent in the past 18 months as domain specific acceleration (dsa) solutions converge onto risc v platforms. The availability of risc v processors with vector extension enabled specialized accelerators to process the layers in between inner loops of the kernel for applications such as artificial intelligence (ai), augmented reality virtual reality (ar vr), and computer vision. Developing processor ip combining risc v defined vector extensions (rvv) with custom dsp instructions promises attractive benefits for low power embedded applications requiring signal processing capabilities. Risc v based edge platforms often combine a control processor (with or without a vector extension) and one or more domain accelerators attached via a memory mapped interconnect.

Domain Specific Accelerators For Risc V Developing processor ip combining risc v defined vector extensions (rvv) with custom dsp instructions promises attractive benefits for low power embedded applications requiring signal processing capabilities. Risc v based edge platforms often combine a control processor (with or without a vector extension) and one or more domain accelerators attached via a memory mapped interconnect.

Domain Specific Accelerators For Risc V

Comments are closed.