Energy Efficient Risc V Based Vector Processor For Cache Aware

Energy Efficient Risc V Based Vector Processor For Cache Aware Based on recent risc v designs, we present in this paper a low power vector processor architecture for efficiently deploying vision transformer (vit) models. to. To overcome these challenges, we propose scalpel that customizes dnn pruning to the underlying hardware by matching the pruned network structure to the data parallel hardware organization. scalpel.

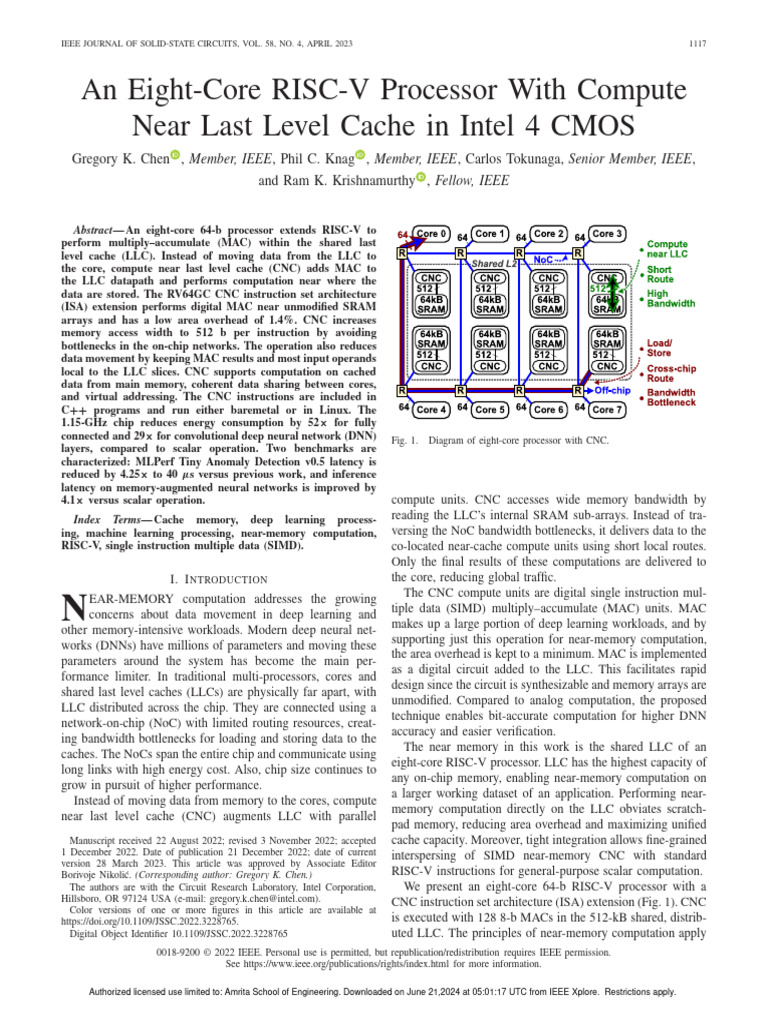

An Eight Core Risc V Processor With Compute Near Last Level Cache In Energy efficient risc v based vector processor for cache aware structurally pruned transformers free download as pdf file (.pdf), text file (.txt) or read online for free. Energy efficient risc v based vector processor for cache aware structurally pruned transformers jung gyu min, dongyun kam, younghoon byun, gunho park, youngjoo lee. Energy efficient risc v based vector processor for cache aware structurally pruned transformers. Bibliographic details on energy efficient risc v based vector processor for cache aware structurally pruned transformers.

Risc V Processor 2 Pdf Central Processing Unit Cpu Cache Energy efficient risc v based vector processor for cache aware structurally pruned transformers. Bibliographic details on energy efficient risc v based vector processor for cache aware structurally pruned transformers. We first introduce vector processing, then detail the memory access patterns specified in the risc v vector extension, and finally examine current vector processor designs and their approaches to memory access handling. Postech oasis repository items in dspace are protected by copyright, with all rights reserved, unless otherwise indicated. It implements the risc v vector extension (rvv) 0.7.1 and can be easily connected to a scalar core using the open vector interface standard. vitruvius natively supports long vectors: 256 double precision floating point elements in a single vector register. Vector architectures are almost unique in their ability to effectively combine high programmability attributes, high computational throughput, and high energy efficiency. this work builds an efficient vector processor that implements the upcoming risc v vector isa extension.

Github Martinriis Risc V Vector Processor 256 Bit Vector Processor We first introduce vector processing, then detail the memory access patterns specified in the risc v vector extension, and finally examine current vector processor designs and their approaches to memory access handling. Postech oasis repository items in dspace are protected by copyright, with all rights reserved, unless otherwise indicated. It implements the risc v vector extension (rvv) 0.7.1 and can be easily connected to a scalar core using the open vector interface standard. vitruvius natively supports long vectors: 256 double precision floating point elements in a single vector register. Vector architectures are almost unique in their ability to effectively combine high programmability attributes, high computational throughput, and high energy efficiency. this work builds an efficient vector processor that implements the upcoming risc v vector isa extension.

Ara A 1 Ghz Scalable And Energy Efficient Risc V Vector Processor It implements the risc v vector extension (rvv) 0.7.1 and can be easily connected to a scalar core using the open vector interface standard. vitruvius natively supports long vectors: 256 double precision floating point elements in a single vector register. Vector architectures are almost unique in their ability to effectively combine high programmability attributes, high computational throughput, and high energy efficiency. this work builds an efficient vector processor that implements the upcoming risc v vector isa extension.

Comments are closed.