Cell Patterning Possibilities For 0a 4f2 Dram

Figure From Novel 4f2 Dram Cell With Vertical Pillar 59 Off This video will briefly discuss the benefits of moving from the 6f2 to 4f2 dram cell architecture and present patterning scenarios for the key cell layers at. This video will briefly discuss the benefits of moving from the 6f2 to 4f2 dram cell architecture and present patterning scenarios for the key cell layers at the 0a (9nm) node. lnkd.in.

Insights Into Advanced Dram Capacitor Patterning Process Window The cell architecture shown in figure 2380a has been evolved from 8f 2 cell to 6f 2 cell since the cell size could be reduced up to 75% at the same design rule (f). Dram is such an important and widely demanded product with today’s surging ai demand, that it’s worth taking a look at how multipatterning with duv would be applied in production. A novel 4f2 dynamic random access memory (dram) cell transistor structure was proposed that can solve various process problems and special failure modes that ca. Fred chen (@drfrederickchen). 6 likes. this video will briefly discuss the benefits of moving from the 6f2 to 4f2 cell architecture and present patterning scenarios for the key cell layers at the 0a (9nm) node.

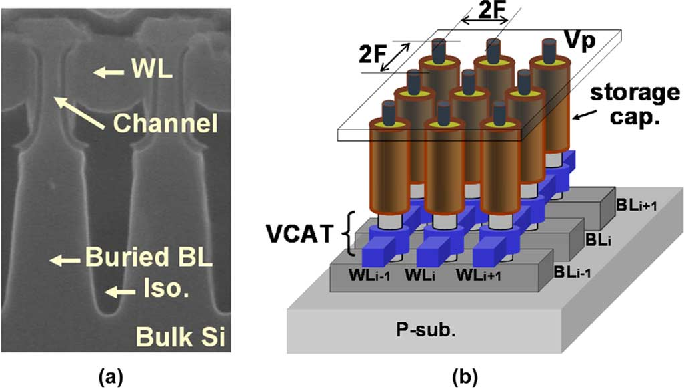

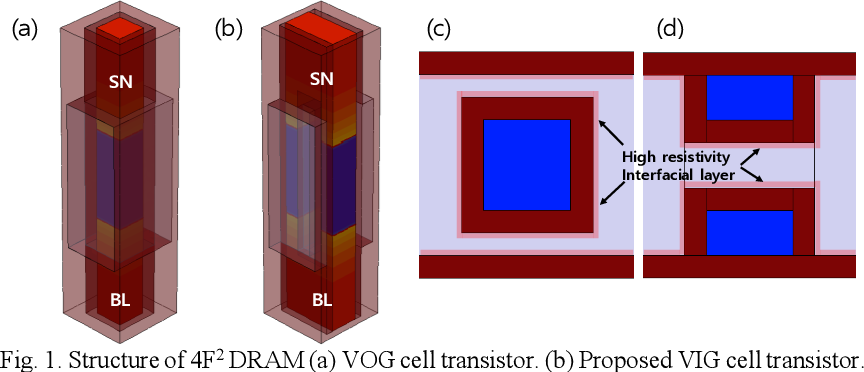

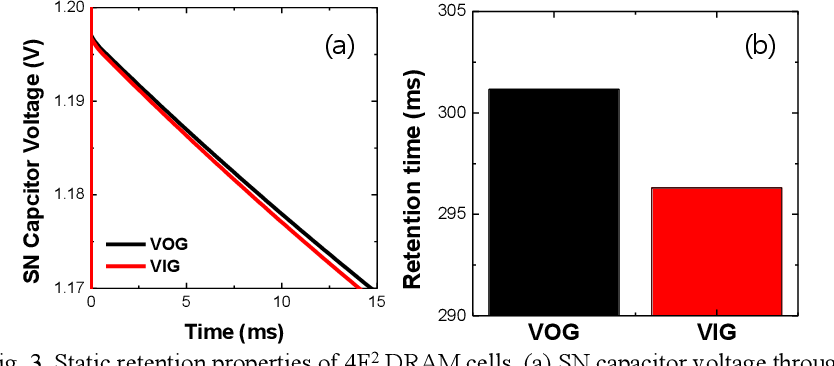

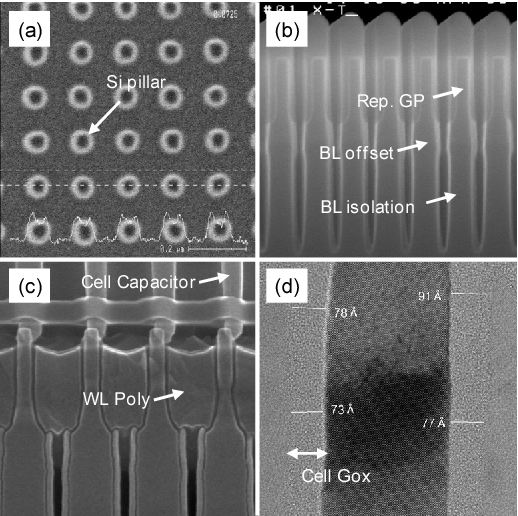

Highly Scalable 4f2 Cell Transistor For Future Dram Technology A novel 4f2 dynamic random access memory (dram) cell transistor structure was proposed that can solve various process problems and special failure modes that ca. Fred chen (@drfrederickchen). 6 likes. this video will briefly discuss the benefits of moving from the 6f2 to 4f2 cell architecture and present patterning scenarios for the key cell layers at the 0a (9nm) node. New type of 4f2 dram: dram is the workhorse memory of electronic systems, but patterning the extremely small features of conventional silicon 6f2 dram memory cells and suppressing “row hammer” electrical interference from nearby cells are major challenges. The layout schematics of the conventional bcat based 6f 2 and the vertical dram based 4f 2 cell arrays are shown in figs. 2 (a) and 2 (b), respectively, demonstrating the higher integration density of the wl, bl, and sn in the 4f 2 array. Using virtual fabrication, we were able to identify some important process parameters that contribute to parasitic defects in a vertical dram and explored the effect of process variability on device performance at both the cell center and the cell edge. It outlines methods to increase dram capacity, including tsv, hybrid bonding, and new cell designs like 1t1c and capacitor less 3d dram. the presentation emphasizes the importance of balancing memory efficiency with performance and error management in ai applications.

Highly Scalable 4f2 Cell Transistor For Future Dram Technology New type of 4f2 dram: dram is the workhorse memory of electronic systems, but patterning the extremely small features of conventional silicon 6f2 dram memory cells and suppressing “row hammer” electrical interference from nearby cells are major challenges. The layout schematics of the conventional bcat based 6f 2 and the vertical dram based 4f 2 cell arrays are shown in figs. 2 (a) and 2 (b), respectively, demonstrating the higher integration density of the wl, bl, and sn in the 4f 2 array. Using virtual fabrication, we were able to identify some important process parameters that contribute to parasitic defects in a vertical dram and explored the effect of process variability on device performance at both the cell center and the cell edge. It outlines methods to increase dram capacity, including tsv, hybrid bonding, and new cell designs like 1t1c and capacitor less 3d dram. the presentation emphasizes the importance of balancing memory efficiency with performance and error management in ai applications.

Figure 4 From Novel 4f2 Dram Cell With Vertical Pillar Transistor Vpt Using virtual fabrication, we were able to identify some important process parameters that contribute to parasitic defects in a vertical dram and explored the effect of process variability on device performance at both the cell center and the cell edge. It outlines methods to increase dram capacity, including tsv, hybrid bonding, and new cell designs like 1t1c and capacitor less 3d dram. the presentation emphasizes the importance of balancing memory efficiency with performance and error management in ai applications.

Comments are closed.