Exploring Semiconductor Process Sensitivity In Vertical Dram A Virtual

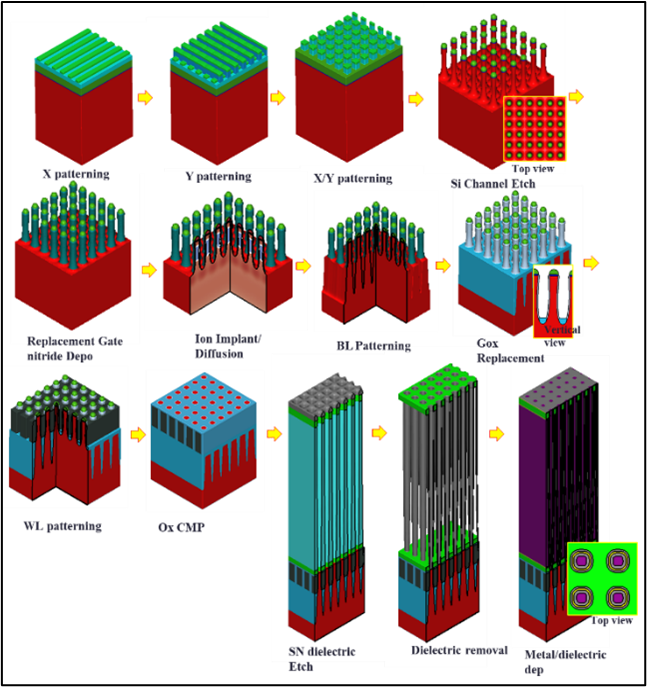

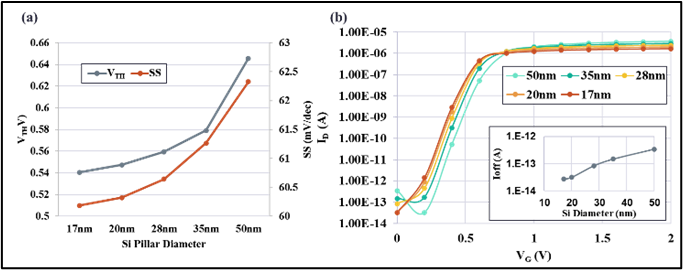

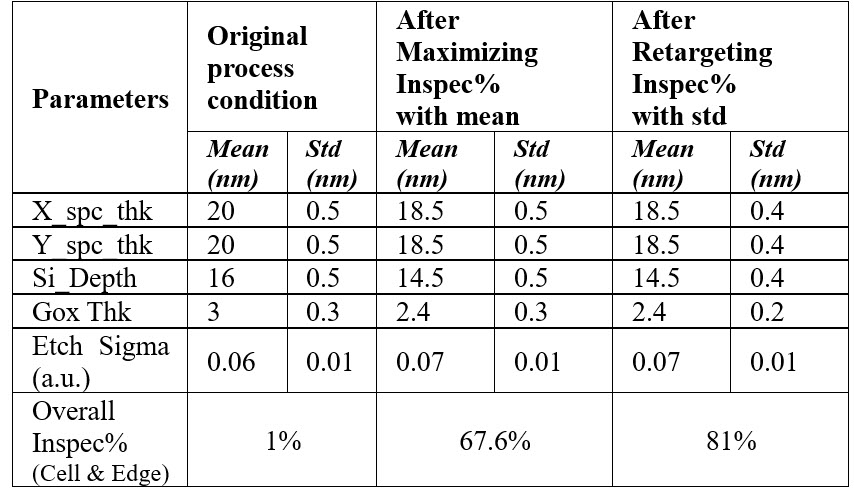

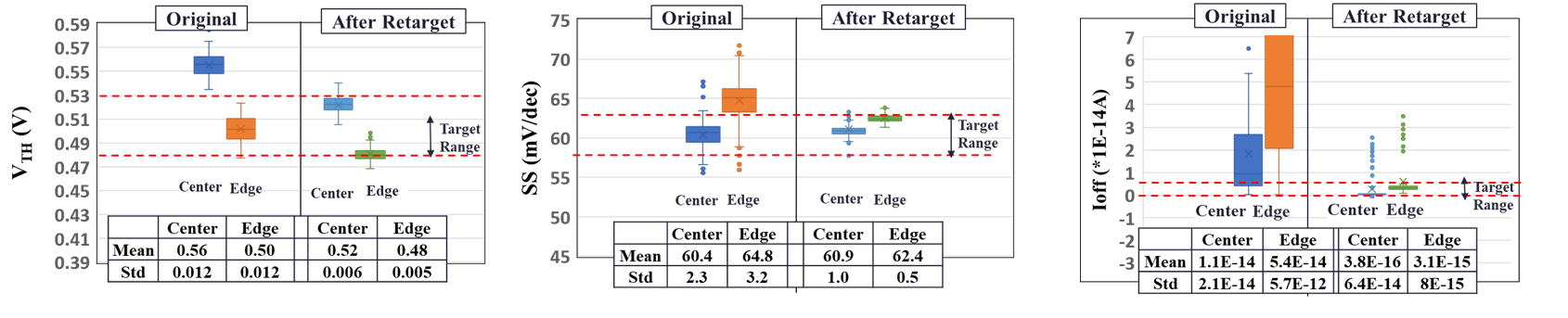

Exploring Semiconductor Process Sensitivity In Vertical Dram A Virtual This article demonstrates a pathfinding technique for a novel vertical dram technology, exploring process parameters, and optimization to improve yield. it discusses the challenges of current dram architectures and the potential of new device architectures. In this article, we demonstrate a pathfinding technique for a novel vertical dram technology. first, we identify important process parameters (defined by current semiconductor production equipment capabilities) that strongly impact yield.

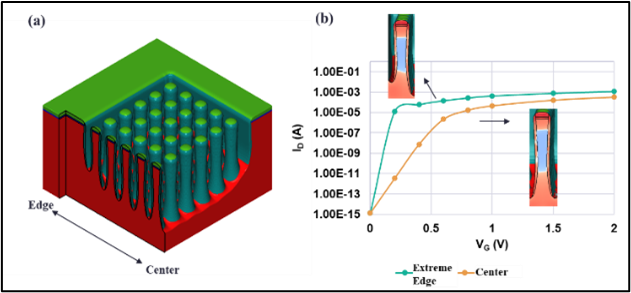

Exploring Semiconductor Process Sensitivity In Vertical Dram A Virtual During this pathfinding process, exploration of potential systematic and parasitic defects can be explored. in this article, we will demonstrate how virtual fabrication can be used to explore semiconductor process sensitivity in a vertical dram architecture. For the past decades, the density of dram has been remarkably increased by making access transistors and capacitors smaller in size per unit area. however, shri. In context: as the technology world craves more and better performing ram with every new manufacturing node generation, dram chips need to follow 3d nand and go vertical. lam research is. In this article, we will demonstrate how virtual fabrication can be used to explore semiconductor process sensitivity in a vertical dram architecture.

Exploring Semiconductor Process Sensitivity In Vertical Dram A Virtual In context: as the technology world craves more and better performing ram with every new manufacturing node generation, dram chips need to follow 3d nand and go vertical. lam research is. In this article, we will demonstrate how virtual fabrication can be used to explore semiconductor process sensitivity in a vertical dram architecture. Dynamic random access memory (dram) device manufacturing explored with tem metrology. see how dram fabrication benefits from characterization. As dram design advances from planar to vertical integration, process control of the recessed gate, generated by etching after patterning in vertical dram, is very critical because of the. Today we will dive into the manufacturing process for finfet, dram, and 3d nand as well as coming changes to that process flow with gate all around, cfet, and 3d dram. In this study, a stable process for preparing 15 periods of vertically stacked si layers from high quality growth to high selectivity and uniform etching is realized, which is a precursor study for multistacking l gaafet and vs cat dram devices.

Exploring Semiconductor Process Sensitivity In Vertical Dram A Virtual Dynamic random access memory (dram) device manufacturing explored with tem metrology. see how dram fabrication benefits from characterization. As dram design advances from planar to vertical integration, process control of the recessed gate, generated by etching after patterning in vertical dram, is very critical because of the. Today we will dive into the manufacturing process for finfet, dram, and 3d nand as well as coming changes to that process flow with gate all around, cfet, and 3d dram. In this study, a stable process for preparing 15 periods of vertically stacked si layers from high quality growth to high selectivity and uniform etching is realized, which is a precursor study for multistacking l gaafet and vs cat dram devices.

Exploring Semiconductor Process Sensitivity In Vertical Dram A Virtual Today we will dive into the manufacturing process for finfet, dram, and 3d nand as well as coming changes to that process flow with gate all around, cfet, and 3d dram. In this study, a stable process for preparing 15 periods of vertically stacked si layers from high quality growth to high selectivity and uniform etching is realized, which is a precursor study for multistacking l gaafet and vs cat dram devices.

Comments are closed.