Write The Verilog Code For The Given Expression Using Dataflow And Behavioral Model

Lab 3 Dataflow And Behavioral Modeling Of Combinational Circuits With This code provides both dataflow and behavioral implementations. the dataflow version is generally preferred for its clarity and efficiency in this specific case. Learn how data flow modeling works in verilog, how to use the assign statement and operators, and its role in designing combinational logic efficiently.

Verilog Dataflow Modeling Pdf The document outlines various verilog design styles, including dataflow, behavioral modeling, and structural modeling, along with their syntax and examples. it also discusses the representation of logic values, the use of operators, and the implementation of case statements for multi way branching. To implement the given expression in verilog, we will first write the dataflow model and then the behavioral model. the expression is y = (ab a'b') (cb ad) (ab'c ac). Learn how to write verilog code for an and gate using gate level, dataflow, and behavioral modeling. this guide includes explanations, verilog examples, rtl schematics, and a testbench for simulation. Audio tracks for some languages were automatically generated. learn more. enjoy the videos and music you love, upload original content, and share it all with friends, family, and the world on.

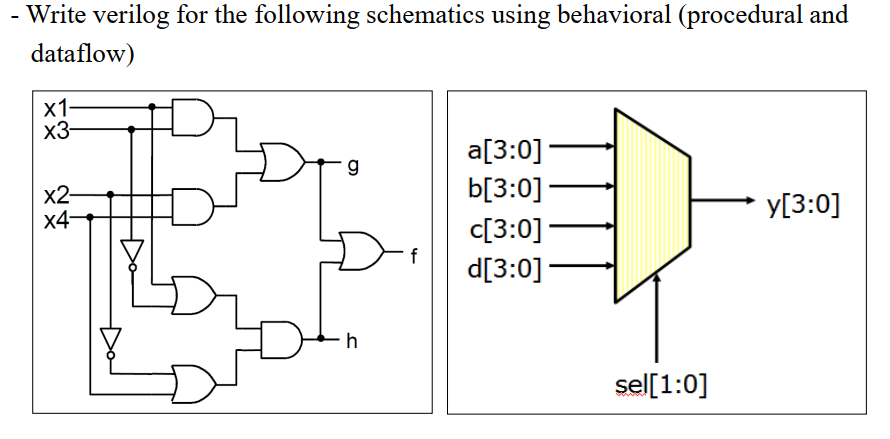

Solved Write Verilog For The Following Schematics Using Chegg Learn how to write verilog code for an and gate using gate level, dataflow, and behavioral modeling. this guide includes explanations, verilog examples, rtl schematics, and a testbench for simulation. Audio tracks for some languages were automatically generated. learn more. enjoy the videos and music you love, upload original content, and share it all with friends, family, and the world on. Dataflow modeling provides the means of describing combinational circuits by their function rather than by their gate structure. dataflow modeling uses a number of operators that act on operands to produce the desired results. This project demonstrates the implementation of a 4 bit adder in verilog using three different modelling styles: behavioral, dataflow, and structural. each implementation is accompanied by a corresponding testbench for simulation and verification. Verilog four valued logic verilog value set consists of four basic values: 0 – represents a logic zero, or false condition 1 – represents a logic one, or true condition x – represents an unknown logic value. Explore behavioral, dataflow, and structural modeling in verilog to design scalable and efficient digital circuits from concept to gate level.

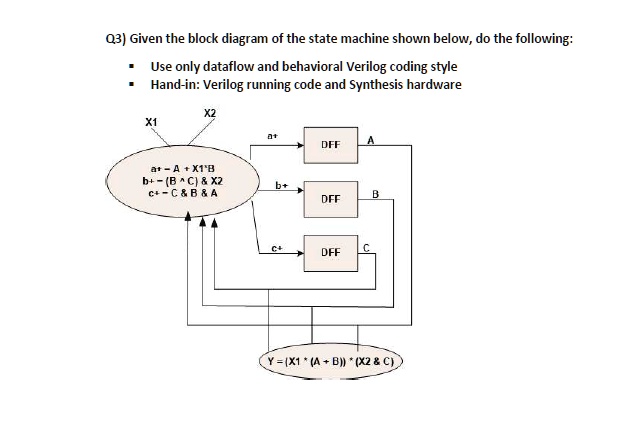

Q3 Given The Block Diagram Of The State Machine Shown Below Do The Dataflow modeling provides the means of describing combinational circuits by their function rather than by their gate structure. dataflow modeling uses a number of operators that act on operands to produce the desired results. This project demonstrates the implementation of a 4 bit adder in verilog using three different modelling styles: behavioral, dataflow, and structural. each implementation is accompanied by a corresponding testbench for simulation and verification. Verilog four valued logic verilog value set consists of four basic values: 0 – represents a logic zero, or false condition 1 – represents a logic one, or true condition x – represents an unknown logic value. Explore behavioral, dataflow, and structural modeling in verilog to design scalable and efficient digital circuits from concept to gate level.

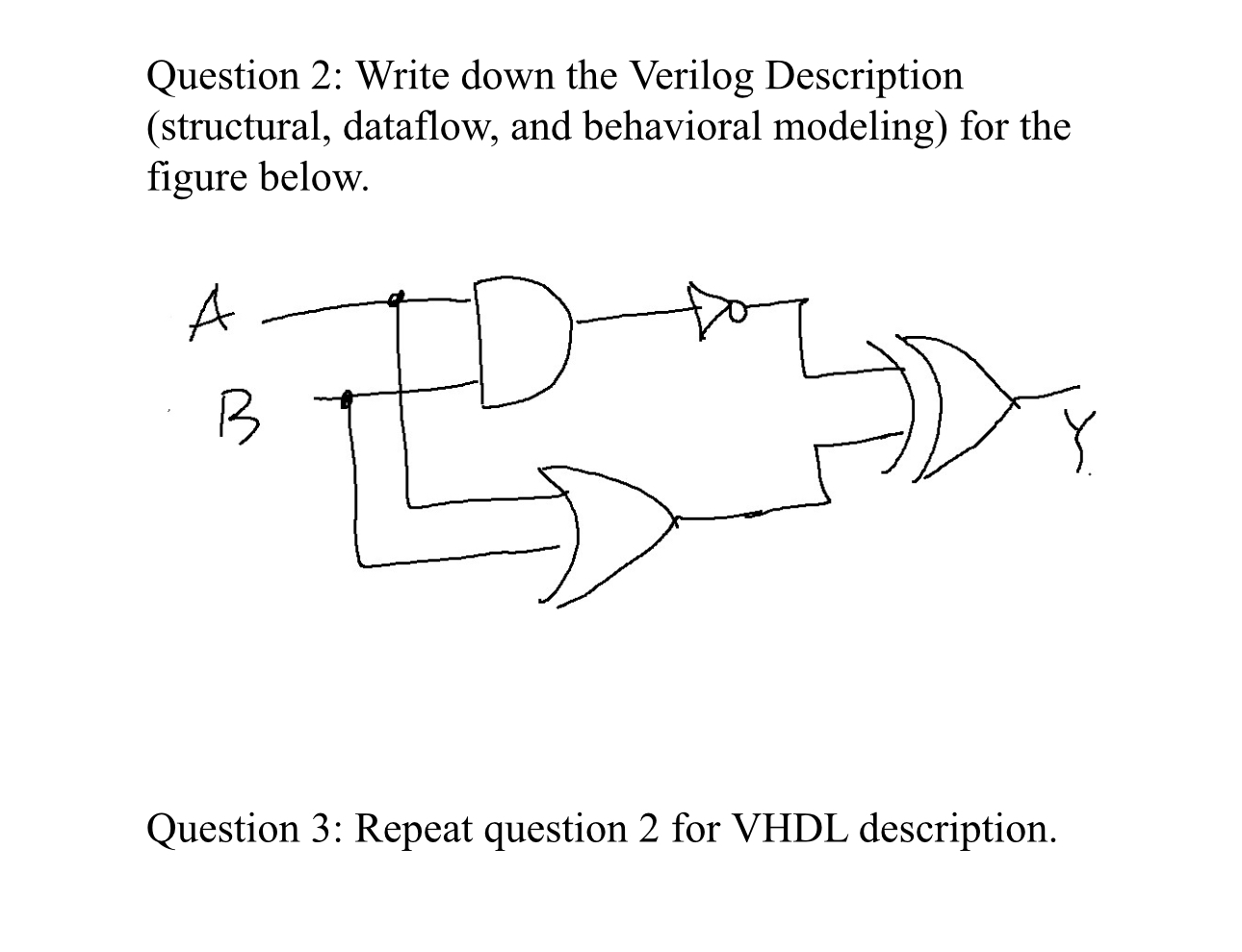

Solved Question 2 Write Down The Verilog Description Chegg Verilog four valued logic verilog value set consists of four basic values: 0 – represents a logic zero, or false condition 1 – represents a logic one, or true condition x – represents an unknown logic value. Explore behavioral, dataflow, and structural modeling in verilog to design scalable and efficient digital circuits from concept to gate level.

Comments are closed.