Vlsi Design Verification Series

Document Moved Testing and verification are essential stages of the vlsi design process, ensuring the correctness, reliability, and manufacturability of integrated circuits. this chapter presents a comprehensive overview of functional verification and manufacturing testing techniques used in modern vlsi systems. Welcome to my collection of vlsi design verification projects. this github repository showcases hands on work in functional verification using verilog, systemverilog, uvm, protocols, and industry standard eda tools.

Vlsi Design Verification Pdf Coverage of all states is impractical even for a design with a few hundred state variables is there a way to identify a subset of state variables that would be tractable, and would lead to better bug detection?. As vlsi designs become increasingly complex, verification has become one of the most time consuming and challenging aspects of the design process. this chapter provides an in depth study of the functional and timing verification algorithms used in vlsi design. This course provides an end to end understanding of vlsi verification — starting from digital design fundamentals and progressing to advanced systemverilog, uvm methodologies, formal verification, power aware verification, and emulation techniques. Learn chip design & verification free tutorials on verilog, systemverilog, uvm, digital design, rtl synthesis and more.

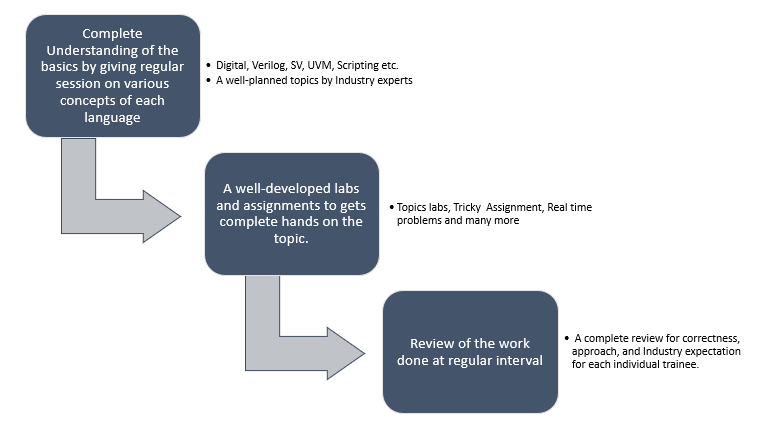

Advance Vlsi Design And Verification This course provides an end to end understanding of vlsi verification — starting from digital design fundamentals and progressing to advanced systemverilog, uvm methodologies, formal verification, power aware verification, and emulation techniques. Learn chip design & verification free tutorials on verilog, systemverilog, uvm, digital design, rtl synthesis and more. With billions of transistors integrated on a single chip, vlsi (very large scale integration) design verification becomes a mission critical step in ensuring that the intended functionality is delivered before fabrication. This document discusses the critical role of verification and testing in the vlsi design flow, highlighting various methodologies employed to ensure chip functionality and quality. This vlsi design verification course includes training on creating test benches with object oriented programming, running constraint random simulations, and achieving verification sign off through functional coverage. In vlsi designs millions of transistors are packed into a single chip, thereby leading to manufacturing defects. so all chips need to be physically tested by providing input signals from a pattern generator and comparing responses using a logic analyzer.

Vlsi Design Verification Pdf With billions of transistors integrated on a single chip, vlsi (very large scale integration) design verification becomes a mission critical step in ensuring that the intended functionality is delivered before fabrication. This document discusses the critical role of verification and testing in the vlsi design flow, highlighting various methodologies employed to ensure chip functionality and quality. This vlsi design verification course includes training on creating test benches with object oriented programming, running constraint random simulations, and achieving verification sign off through functional coverage. In vlsi designs millions of transistors are packed into a single chip, thereby leading to manufacturing defects. so all chips need to be physically tested by providing input signals from a pattern generator and comparing responses using a logic analyzer.

Best Vlsi Training In Hyderabad Top Vlsi Institutes Courses 2025 This vlsi design verification course includes training on creating test benches with object oriented programming, running constraint random simulations, and achieving verification sign off through functional coverage. In vlsi designs millions of transistors are packed into a single chip, thereby leading to manufacturing defects. so all chips need to be physically tested by providing input signals from a pattern generator and comparing responses using a logic analyzer.

Comments are closed.