Verilog Tutorial Umd Verilog Tutorial Umd Pdf Pdf4pro

Verilog Tutorial Pdf Verilog is one of the hdl languages available in theindustry for designing the hardware . verilog allows us to design a digital design at behavior level,register transfer level (rtl), gate level and at switch level. Verilog is one of the hdl languages available in the industry for designing the hardware. verilog allows us to design a digital design at behavior level, register transfer level (rtl), gate level and at switch level.

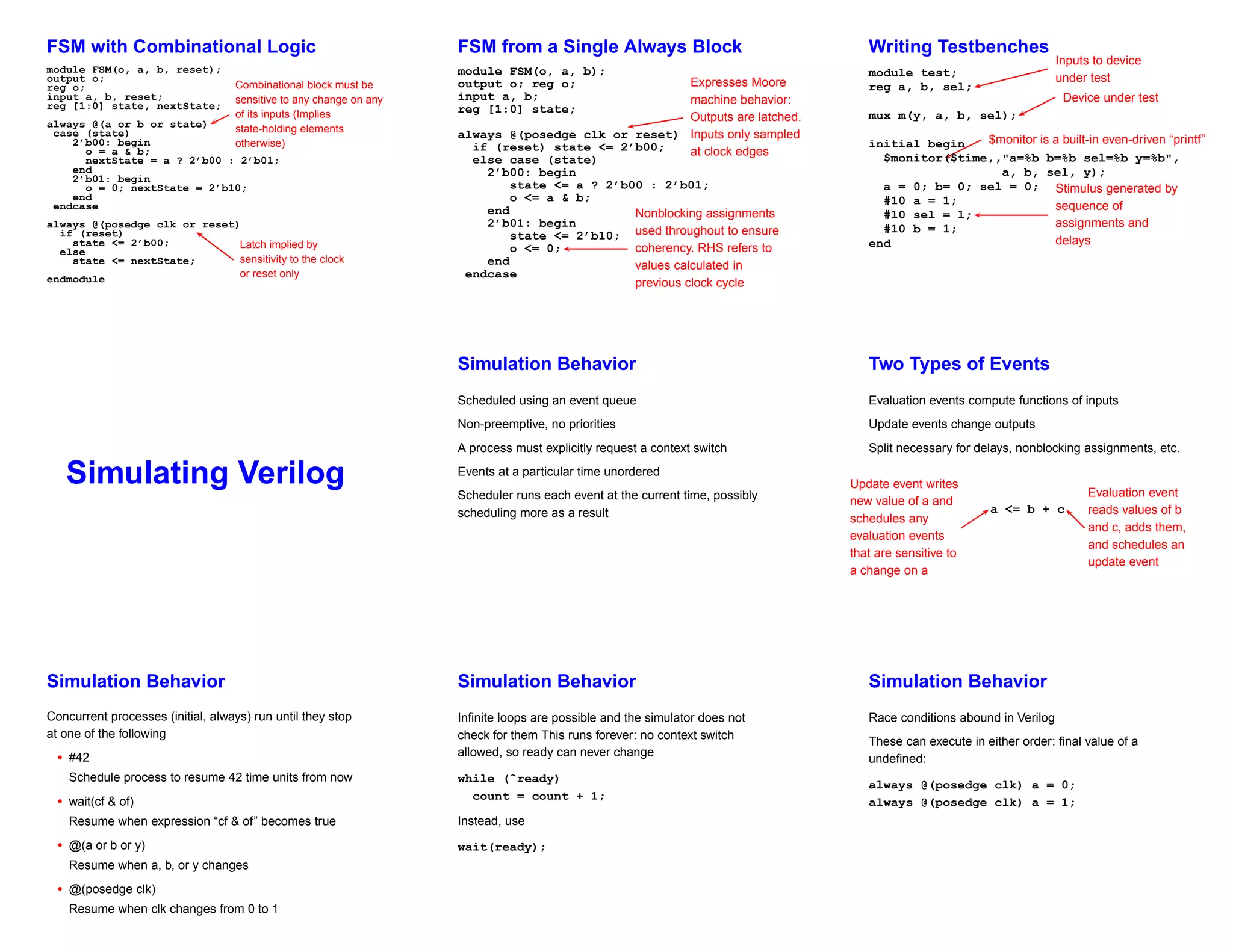

Verilog Cheat Sheet 1672542963 Pdf Verilog is a hardware description language (hdl) that enables engineers to describe, simulate, and synthesize digital circuits using text based code. this comprehensive tutorial will guide you from basic concepts to practical applications in modern chip design. Loading…. Verilog tutorial.pdf free download as pdf file (.pdf), text file (.txt) or read online for free. This page contains verilog tutorial, verilog syntax, verilog quick reference, pli, modelling memory and fsm, writing testbenches in verilog, lot of verilog examples and verilog in one day tutorial.

Introduction To Verilog Pdf Hardware Description Language Logic Gate Verilog tutorial.pdf free download as pdf file (.pdf), text file (.txt) or read online for free. This page contains verilog tutorial, verilog syntax, verilog quick reference, pli, modelling memory and fsm, writing testbenches in verilog, lot of verilog examples and verilog in one day tutorial. Verilog is a language that includes special features for circuit modeling and simulation. in this course, we will employ only a simple subset of verilog. in fact, we will focus just on those language constructs used for “structural composition”—sometimes also referred to as “gate level modeling”. There are many different ways to write verilog code, and some are better than others. it covers modelling clocks, state machines, pipelines, 0 delay code, and race conditions, as well as efficient coding techniques. The implementation was the verilog simulator sold by gateway. the first major extension was verilog xl, which added a few features and implemented the infamous "xl algorithm" which was a very efficient method for doing gate level simulation. This manual introduces the basic and most common verilog behavioral and gate level modelling constructs, as well as verilog compiler directives and system functions.

Basic Verilog Basic Verilog Pdf Pdf4pro Verilog is a language that includes special features for circuit modeling and simulation. in this course, we will employ only a simple subset of verilog. in fact, we will focus just on those language constructs used for “structural composition”—sometimes also referred to as “gate level modeling”. There are many different ways to write verilog code, and some are better than others. it covers modelling clocks, state machines, pipelines, 0 delay code, and race conditions, as well as efficient coding techniques. The implementation was the verilog simulator sold by gateway. the first major extension was verilog xl, which added a few features and implemented the infamous "xl algorithm" which was a very efficient method for doing gate level simulation. This manual introduces the basic and most common verilog behavioral and gate level modelling constructs, as well as verilog compiler directives and system functions.

Verilog Tutorial 3 Kien 082009 Pdf Integrated Circuit Field The implementation was the verilog simulator sold by gateway. the first major extension was verilog xl, which added a few features and implemented the infamous "xl algorithm" which was a very efficient method for doing gate level simulation. This manual introduces the basic and most common verilog behavioral and gate level modelling constructs, as well as verilog compiler directives and system functions.

Comments are closed.