Verify Generated Code Using Hdl Test Bench At Command Line Matlab

Verify Generated Code Using Hdl Test Bench From Configuration This example shows how to generate a hdl test bench and verify the generated code for your design. the example assumes that you have already generated hdl code for your model. The tutorial provides instructions to run hdl cosimulation with matlab and simulink, perform fpga validation using fpga in the loop simulation, and load signals from designs programmed into development boards into matlab using fpga data capture.

Generate Hdl Code From Matlab Code By Using Native Floating Point And Generate a test bench that verifies generated hdl code against test vectors from simulink. This test bench verifies the generated hdl dut against a c representation of the source simulink model. see verify hdl design using systemverilog dpi test bench. This example shows how to generate a hdl test bench and verify the generated code for your design. the example assumes that you have generated hdl code for your model. Generate test bench and code coverage for generated hdl code using the hdl workflow advisor.

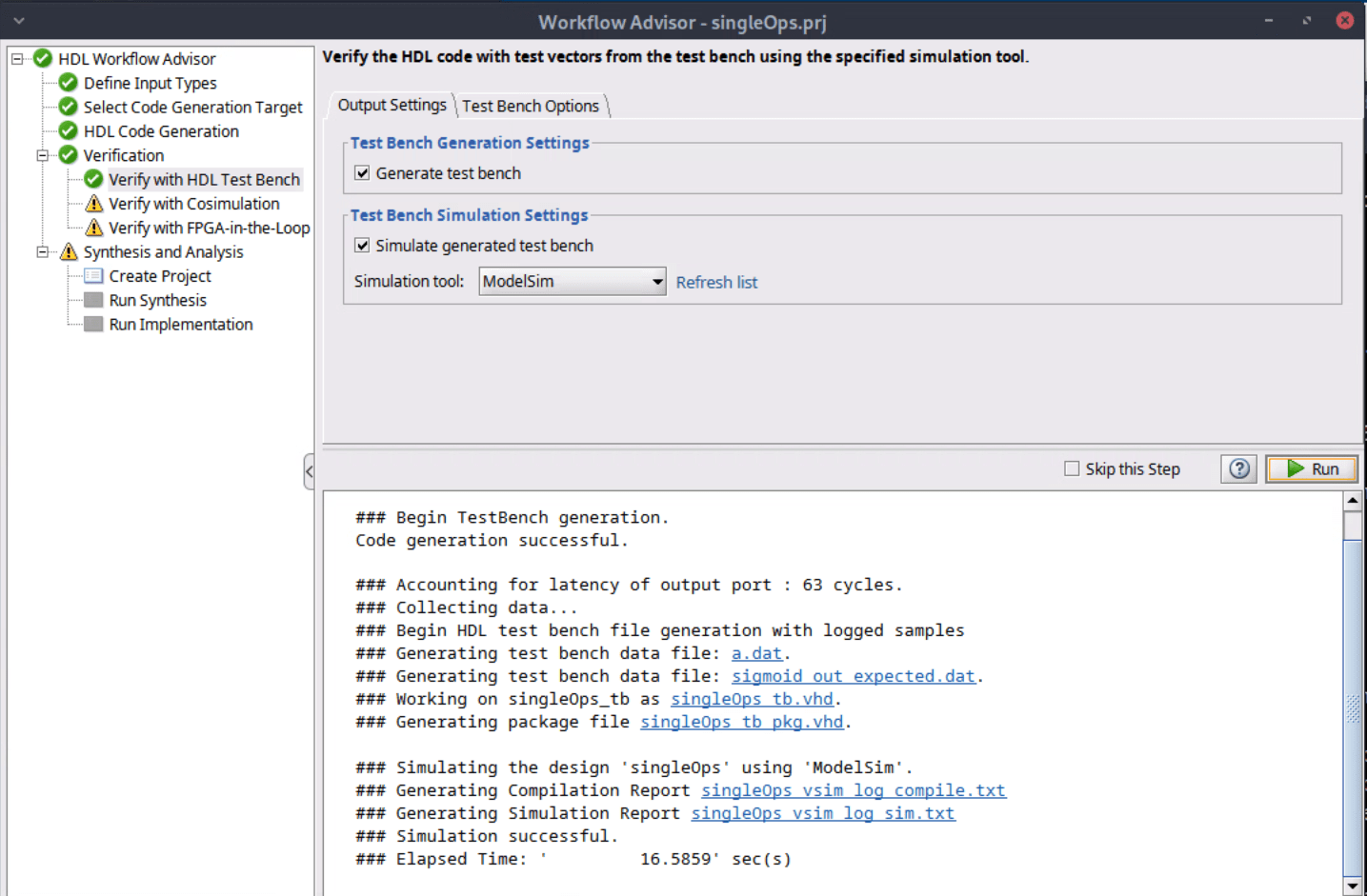

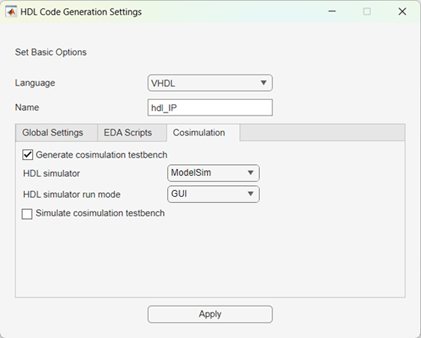

Generate And Verify Hdl Code With Dsp Hdl Ip Designer App Matlab This example shows how to generate a hdl test bench and verify the generated code for your design. the example assumes that you have generated hdl code for your model. Generate test bench and code coverage for generated hdl code using the hdl workflow advisor. You can generate the test bench files and verify the numeric behavior of the generated high level synthesis code to the matlab ® code by using the hdl test bench. Simulate the generated hdl design under test (dut) with test vectors from the test bench using the specified simulation tool. The code generator generates an hdl test bench by running a simulink simulation to capture input vectors and expected output data for your dut. you should connect appropriate stimulus or source blocks to the input ports of the dut to generate a testbench with valid inputs. The hdl test bench parameter enables or disables the hdl test bench generation. the code generator creates a hdl test bench by running a simulink ® simulation that captures input vectors and expected output data for your dut.

Generate Hdl Code From Matlab Matlab Simulink You can generate the test bench files and verify the numeric behavior of the generated high level synthesis code to the matlab ® code by using the hdl test bench. Simulate the generated hdl design under test (dut) with test vectors from the test bench using the specified simulation tool. The code generator generates an hdl test bench by running a simulink simulation to capture input vectors and expected output data for your dut. you should connect appropriate stimulus or source blocks to the input ports of the dut to generate a testbench with valid inputs. The hdl test bench parameter enables or disables the hdl test bench generation. the code generator creates a hdl test bench by running a simulink ® simulation that captures input vectors and expected output data for your dut.

Comments are closed.