Understanding The Systemverilog String Data Type

Understanding The Systemverilog String Data Type Learn how to use systemverilog's string data type and built in methods like len (), putc (), toupper (), and compare () to manipulate text data. Learn how to use systemverilog strings with simple easy to understand code example. learn string manipulations, methods & operators execute in browser!.

Signed Data Type In Verilog Learn systemverilog constants and strings with practical examples. compare macros, parameters, and const variables. includes string methods. Systemverilog methods and utilities to manipulate systemverilog strings here’s a cheatsheet with systemverilog string method. you can play with this example on eda playground. String data types come with build in methods. equality. checks if the two strings are equal. result is 1 if they are equal and 0 if they are not. both strings can be of type string. or one of them can be a string literal. if both operands are string literals, the expression is the same verilog equality operator for integer types. The string type in systemverilog allows you to store sequences of characters. strings are useful in verification environments for displaying messages or storing configuration data.

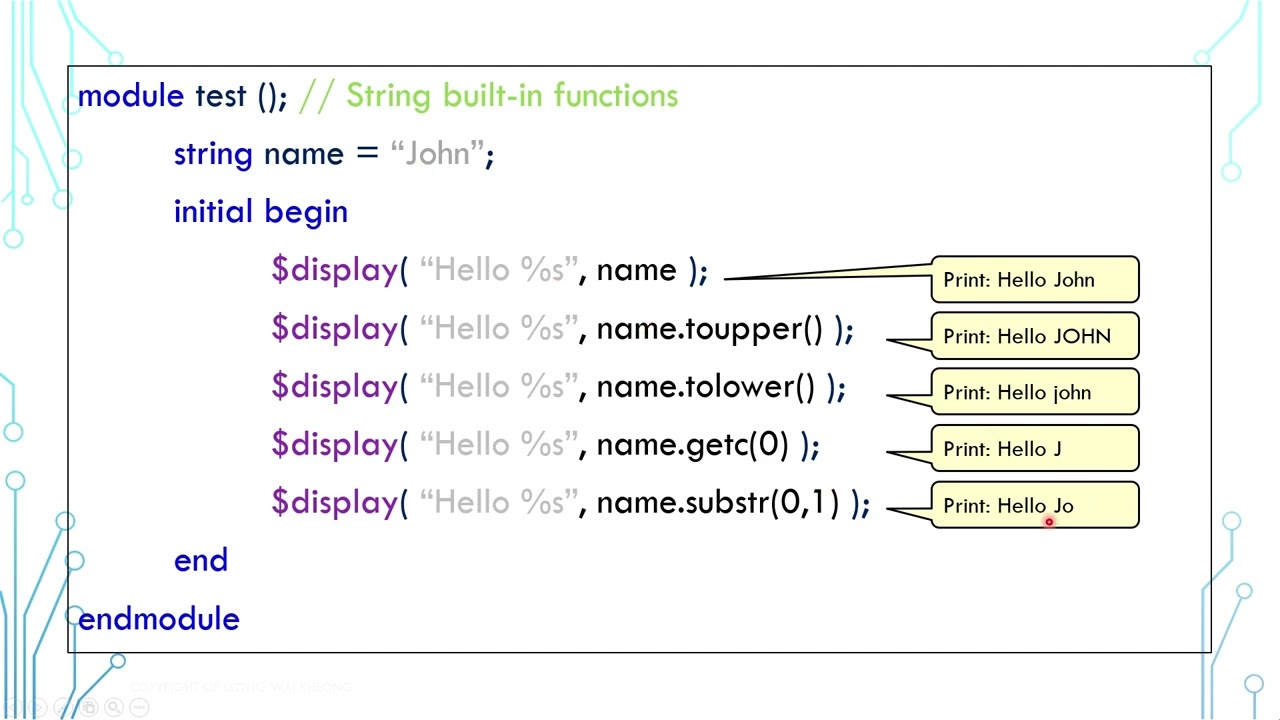

Understanding Data Types In Systemverilog Vlsi Worlds String data types come with build in methods. equality. checks if the two strings are equal. result is 1 if they are equal and 0 if they are not. both strings can be of type string. or one of them can be a string literal. if both operands are string literals, the expression is the same verilog equality operator for integer types. The string type in systemverilog allows you to store sequences of characters. strings are useful in verification environments for displaying messages or storing configuration data. Welcome to this quick tutorial on string variables in systemverilog. in just five minutes, we will explore how to effectively use string variables, their built in functions, and file i o operations. In system verilog, the string data type can be used to store strings. string also provides various methods which are helpful for string operations like finding the length of string, etc. Traditional veriog only supports strings in literal representation, while systemverilog uses strings as a built in data type. similar to c 's std::string type, the systemverilog string type supports many operations and functions. The reg type holds their values until another value is put on them, just like a register hardware component. the declarations for wire and reg signals are inside a module but outside any initial or always block.

Understanding String Variables In Systemverilog A Quick Guide Galaxy Ai Welcome to this quick tutorial on string variables in systemverilog. in just five minutes, we will explore how to effectively use string variables, their built in functions, and file i o operations. In system verilog, the string data type can be used to store strings. string also provides various methods which are helpful for string operations like finding the length of string, etc. Traditional veriog only supports strings in literal representation, while systemverilog uses strings as a built in data type. similar to c 's std::string type, the systemverilog string type supports many operations and functions. The reg type holds their values until another value is put on them, just like a register hardware component. the declarations for wire and reg signals are inside a module but outside any initial or always block.

Understanding String Variables In Systemverilog A Quick Guide Galaxy Ai Traditional veriog only supports strings in literal representation, while systemverilog uses strings as a built in data type. similar to c 's std::string type, the systemverilog string type supports many operations and functions. The reg type holds their values until another value is put on them, just like a register hardware component. the declarations for wire and reg signals are inside a module but outside any initial or always block.

Understanding String Variables In Systemverilog A Quick Guide Galaxy Ai

Comments are closed.