Test Your Ecc Ram Error Detection And Correction Capabilities

The Capability Of Error Detection Or And Error Correction For Each Ecc The passmark ecc tester is an ddr4 dimm interposer, designed to inject single bit and double bit errors in real time, to challenge and test the error detection and correction mechanism of machines that have cpu, motherboard and ram sticks with ecc support. The passmark ecc tester is an ddr4 dimm interposer, designed to inject single bit and double bit errors in real time, to challenge and test the error detection and correction mechanism.

Ecc Ram Network Encyclopedia The passmark ecc tester is an ddr4 dimm interposer, designed to inject single bit and double bit errors in real time, to challenge and test the error detection and correction mechanism of machines that have cpu, motherboard and ram sticks with ecc support. Learn how to detect, monitor and log memory corruption using ecc ram on linux. The passmark ecc tester is an ddr4 dimm interposer, designed to inject single bit and double bit errors in real time, to challenge and test the error detection and correction mechanism of machines that have cpu, motherboard and ram sticks with ecc support. The processor provides error checking and correction (ecc) data hardware. the ecc bits are computed on 32 bit data sets; they are computed and then stored in memory with the data. when the data is accessed, the hardware can detect one and two bit errors within the 32 bit data and its ecc bits.

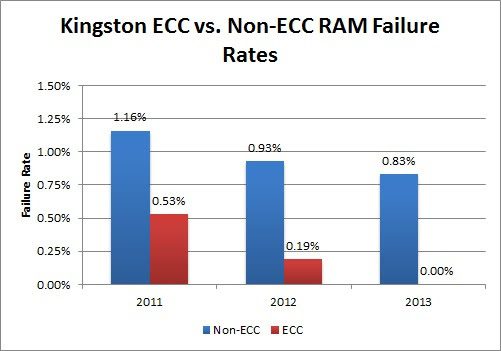

Ecc Ram Everything You Need To Know About It Deskdecode Com The passmark ecc tester is an ddr4 dimm interposer, designed to inject single bit and double bit errors in real time, to challenge and test the error detection and correction mechanism of machines that have cpu, motherboard and ram sticks with ecc support. The processor provides error checking and correction (ecc) data hardware. the ecc bits are computed on 32 bit data sets; they are computed and then stored in memory with the data. when the data is accessed, the hardware can detect one and two bit errors within the 32 bit data and its ecc bits. A server board should log soft and hard ecc errors into its hardware log (hard errors would also display in memtest86). you should be able to check the log after a test period either through the bios menu or using additional system tools provided by the board vendor. The l2 memory controller provides edc with a hamming code capable of detecting double bit errors and correcting single bit errors within each 128 bit word. edc is supported for both l2 ram and l2 cache accesses. Ecc ram detects and corrects memory errors, keeping servers and critical systems stable. compare it with non ecc ram, explore pros, cons, and real use cases. I am implementing ecc self test for ram for rh850 (r7f701374). during implementation, i’ve successfully enabled ecc test mode using the lrtstctl register to inject single bit errors by modifying ram data directly without updating ecc bits.

Ecc Ram Everything You Need To Know About It Deskdecode Com A server board should log soft and hard ecc errors into its hardware log (hard errors would also display in memtest86). you should be able to check the log after a test period either through the bios menu or using additional system tools provided by the board vendor. The l2 memory controller provides edc with a hamming code capable of detecting double bit errors and correcting single bit errors within each 128 bit word. edc is supported for both l2 ram and l2 cache accesses. Ecc ram detects and corrects memory errors, keeping servers and critical systems stable. compare it with non ecc ram, explore pros, cons, and real use cases. I am implementing ecc self test for ram for rh850 (r7f701374). during implementation, i’ve successfully enabled ecc test mode using the lrtstctl register to inject single bit errors by modifying ram data directly without updating ecc bits.

Importanta Ecc In Detectarea Si Corectarea Erorilor Ram Adata Ecc ram detects and corrects memory errors, keeping servers and critical systems stable. compare it with non ecc ram, explore pros, cons, and real use cases. I am implementing ecc self test for ram for rh850 (r7f701374). during implementation, i’ve successfully enabled ecc test mode using the lrtstctl register to inject single bit errors by modifying ram data directly without updating ecc bits.

Comments are closed.