System Verilog Datatypes Pdf Data Type Queue Abstract Data Type

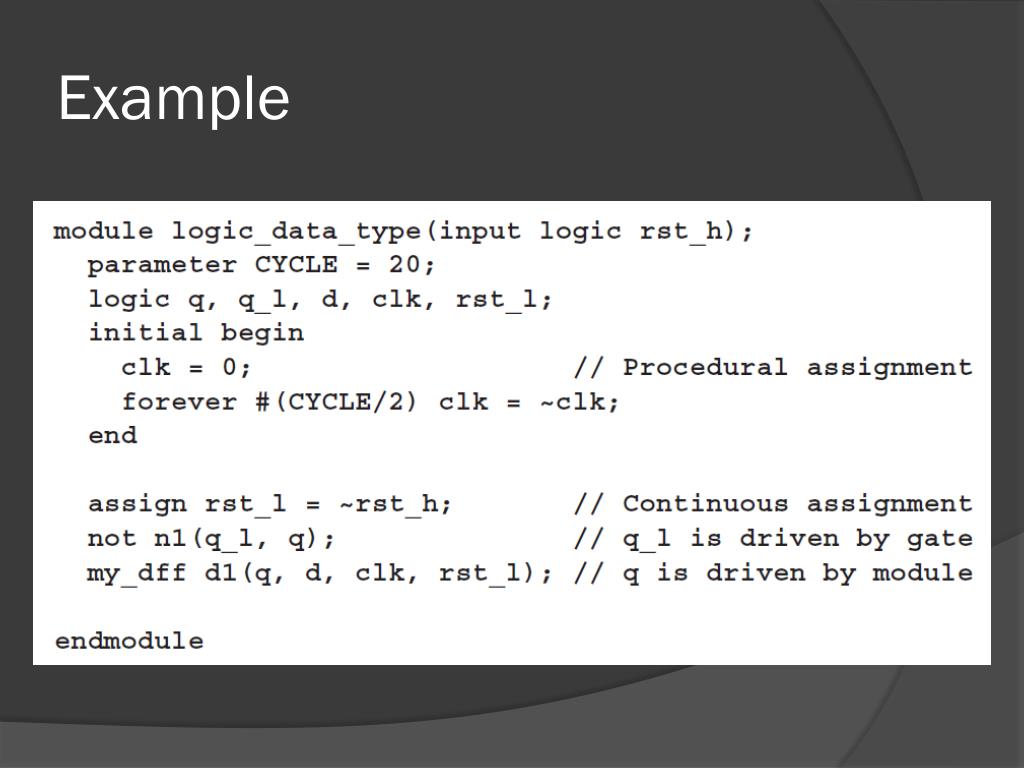

System Verilog Data Type Pdf Integer Computer Science Queue System verilog supports various data types including: two state and queue types for better performance and memory usage. classes, structures, unions and packed structures for abstract data structures. System verilog data type free download as pdf file (.pdf), text file (.txt) or read online for free. the document discusses various system verilog data types including wire, reg, logic, integer, real, bit, byte, short int, string, event, and arrays.

System Verilog Datatypes Pdf Data Type Queue Abstract Data Type This document summarizes different data types in systemverilog including: 1) structural types like wire and reg that model hardware connections; 2) behavioral types like integer, real, and time for simulation; 3) parameters for constants; 4) logic type; 5) two state types like bit and byte; 6) void for non existent data; and 7) user defined. • • the classic verilog way to create a constant is with a text macro. • on the plus side, macros have global scope and can be used for bit field definitions and type definitions. • on the negative side, macros are global, so that they can cause conflicts if you just need a local constant. Systemverilog is an enhanced version of verilog that integrates design, verification, and scalability features, making it more powerful for hardware modeling. it introduces advanced data types, object oriented programming support, and improved inter process communication tools. Learn all about the different newly introduced systemverilog data types like logic, unsigned, string with simple examples systemverilog tutorial for beginners.

Lecture5 System Verilog Advanced Datatypes Pdf Pdf Array Data Systemverilog is an enhanced version of verilog that integrates design, verification, and scalability features, making it more powerful for hardware modeling. it introduces advanced data types, object oriented programming support, and improved inter process communication tools. Learn all about the different newly introduced systemverilog data types like logic, unsigned, string with simple examples systemverilog tutorial for beginners. System verilog offers improved data types like 4 state, 2 state, real, and user defined types. it also supports arrays, structures, unions, and other data structures. system verilog enables robust hardware verification through features like assertions, coverage, randomization, and dynamic processes. we take content rights seriously. Datatypes : 2 state , 4 state array: fixed, queue and dynamic array array initialization loops for array queue method demonstration of fixed size array and queue implementing simple 2:1 mux implementing a full adder consisting of two half adders understanding usage of an array array initialization strategies loops for. Systemverilog offers many improved data structures compared with verilog. some of these were created for designers but are also useful for testbenches. in this chapter you will learn about the data structures most useful for verification. The document discusses various data types in system verilog, contrasting them with verilog 95 types. it outlines the distinctions between 4 state and 2 state data types, array types including fixed and dynamic arrays, and user defined types, including enumerated types and their applications.

Abstract Data Types Arrays And Queues Pdf Queue Abstract Data System verilog offers improved data types like 4 state, 2 state, real, and user defined types. it also supports arrays, structures, unions, and other data structures. system verilog enables robust hardware verification through features like assertions, coverage, randomization, and dynamic processes. we take content rights seriously. Datatypes : 2 state , 4 state array: fixed, queue and dynamic array array initialization loops for array queue method demonstration of fixed size array and queue implementing simple 2:1 mux implementing a full adder consisting of two half adders understanding usage of an array array initialization strategies loops for. Systemverilog offers many improved data structures compared with verilog. some of these were created for designers but are also useful for testbenches. in this chapter you will learn about the data structures most useful for verification. The document discusses various data types in system verilog, contrasting them with verilog 95 types. it outlines the distinctions between 4 state and 2 state data types, array types including fixed and dynamic arrays, and user defined types, including enumerated types and their applications.

Verilog Data Types A Simple Guide For Beginners 2025 Systemverilog offers many improved data structures compared with verilog. some of these were created for designers but are also useful for testbenches. in this chapter you will learn about the data structures most useful for verification. The document discusses various data types in system verilog, contrasting them with verilog 95 types. it outlines the distinctions between 4 state and 2 state data types, array types including fixed and dynamic arrays, and user defined types, including enumerated types and their applications.

Signed Data Type In Verilog

Comments are closed.