System Verilog Cheat Sheet Computer Architecture Arithmetic

Verilog Cheat Sheet A Concise Guide To Verilog Syntax Operators And This repository serves as a comprehensive cheat sheet for various verilog modules related to computer organization and architecture (coa). it provides ready to use verilog code snippets for different components, facilitating quick reference and implementation. In this instance the function input is zero, to the synthesis system is likely to simplify the implemen tation of this instance so that it is only capable of performing an addition (the zero case).

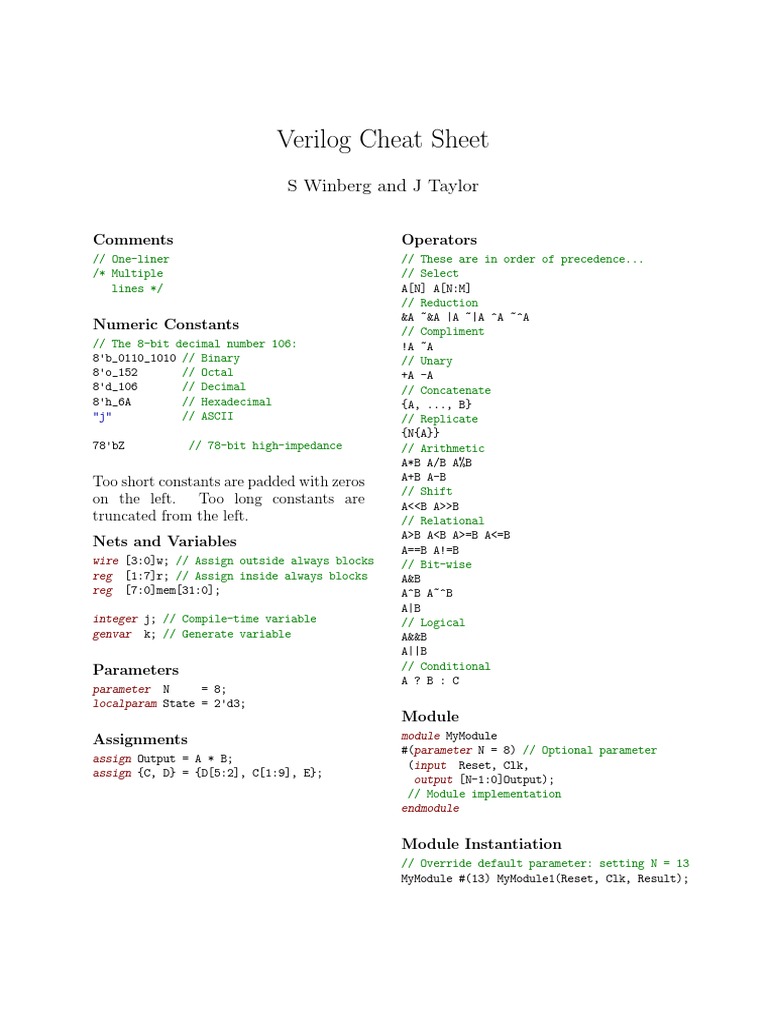

Computer Architecture Cheat Sheet Pdf Computer Hardware Computer Data The document provides an overview of synthesisable systemverilog, detailing the use of numbers, constants, and various operators for assignments in hardware design. it explains continuous assignments, the use of always ff and always comb blocks, and how to declare registers and wires. The goal of this paper is to reveal many of the mysteries of verilog and systemverilog, and help engineers understand the important underlying rules of the verilog and systemverilog languages. System tasks for simulation outputs once when encountered ( newline) outputs once when encountered (no newline) outputs anytime one of its signal changes ( newline) returns current time (in time format). Verilog cheatsheet a comprehensive cheat sheet for verilog, covering syntax, data types, operators, and common constructs. useful for digital design and hardware verification.

Verilog Cheet Sheet Pdf System tasks for simulation outputs once when encountered ( newline) outputs once when encountered (no newline) outputs anytime one of its signal changes ( newline) returns current time (in time format). Verilog cheatsheet a comprehensive cheat sheet for verilog, covering syntax, data types, operators, and common constructs. useful for digital design and hardware verification. Use arr.min()[0] to get the value. use foreach(arr[i]) instead of for loops cleaner and works with all array types. Note : here you have to select the topic for which you need verilog code and you will be directly shifted to that code. in the coding area in the right hand side top corner, you will find a button named "copy", you can just select that and copy the entire code to your clipboard. Ee 201 systemverilog reference sheet gray italics represent user defined names or operations purple constructs are only for simulation (at least in this course) this is a comment * multi line comment * separated by commas module module name ( input logic port name, single bit input. 1. introduction and python for functional level modeling, verification, and simulator harnesses. this tutorial briefly reviews the basics of the verilog hardware description language, but primaril focuses on how we can integrate verilog rtl modeling into our pymtl3 framework. the tutorial also in clu.

Comments are closed.