Stacking Chips Using 3d Heterogeneous Integration

Heterogeneous Integration Stacking Process Download Scientific Diagram Unlike traditional two dimensional integrated circuits, which spread components across a flat surface, 3d ics utilize the vertical dimension to stack and interconnect multiple layers of active electronic components. This book explains for readers how 3d chip stacks promise to increase the level of on chip integration, and to design new heterogeneous semiconductor devices that combine chips of different integration technologies (incl. sensors) in a single package of the smallest possible size.

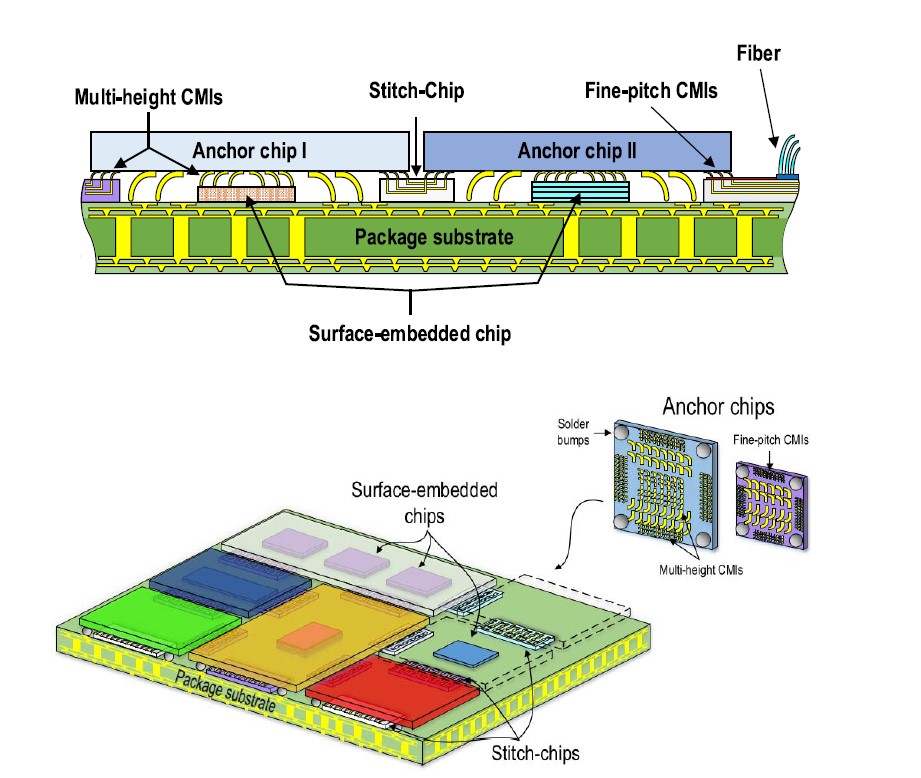

Common Heterogeneous Integration And Ip Reuse Strategies Chips 3d 3d heterogeneous integration currently exists with heat sinks or cold plates that are inadequate for thermal management of 3d stacks of high power chips due to their inability to cool the chips in the middle and bottom of the stack. There are several complementary approaches to 3d integration. for example, 3d heterogeneous integration involves stacking and interconnecting multiple chips, each potentially made. Increasing the number of transistors you can squeeze into a given area by stacking up chips (called chiplets in this case) is both the present and future of silicon. Design teams across the globe are just starting to make sense of this new future of semiconductor design, which will require a deep understanding of the tradeoffs and growing list of options available in a 3d heterogeneous design.

Heterogeneous Integration 2 5d And 3d Integrated 3d Systems Group Increasing the number of transistors you can squeeze into a given area by stacking up chips (called chiplets in this case) is both the present and future of silicon. Design teams across the globe are just starting to make sense of this new future of semiconductor design, which will require a deep understanding of the tradeoffs and growing list of options available in a 3d heterogeneous design. A novel power supply technology for 3d integrated chips has been developed by employing a three dimensionally stacked computing architecture consisting of processing units placed directly above stacks of dynamic random access memory. Our reconfigurable three dimensional hetero integrated technology can be used to vertically stack a diverse range of functional layers and could provide energy efficient sensor computing. The integration of the gaas rf chip and the si cmos digital chip is realized through 3d heterogeneous stacking. the si cmos chip is flipped and precisely aligned with the gaas rf chip using a high precision flip chip bonder. There are several methods for 3d ic design, including recrystallization and wafer bonding methods.

Comments are closed.