Sound Jitter Simulation

Jitter Prompt Giddyhead Sound Avenue Digital audio assumes perfectly spaced samples in time. but in reality, clock imperfections cause samples to land a few microseconds early or late—this is jitter. Jitter mode (at least the "pmjitter" mode) uses the "time domain" noise feature of pnoise analysis. this works by adding an ideal sampler at the output of the circuit, and then observing the noise at that instant in time.

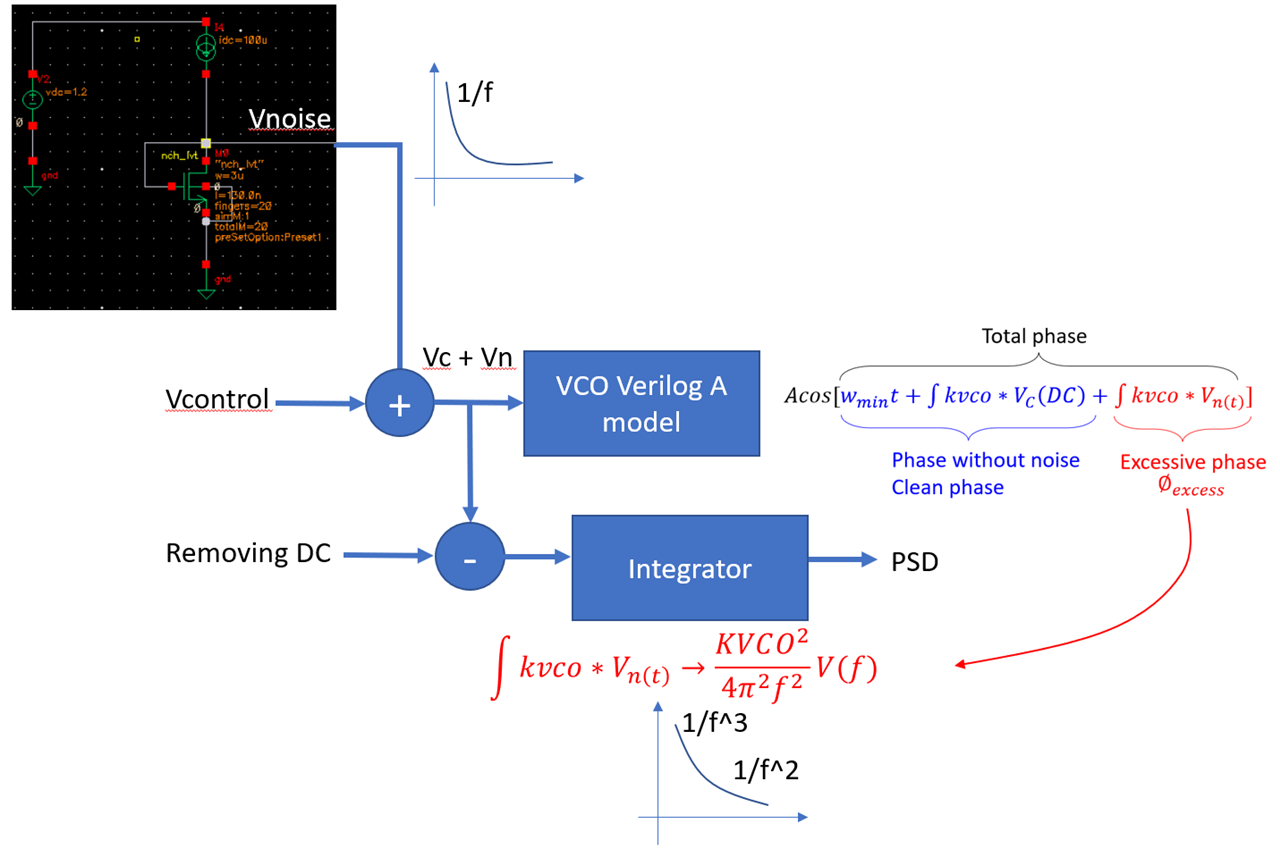

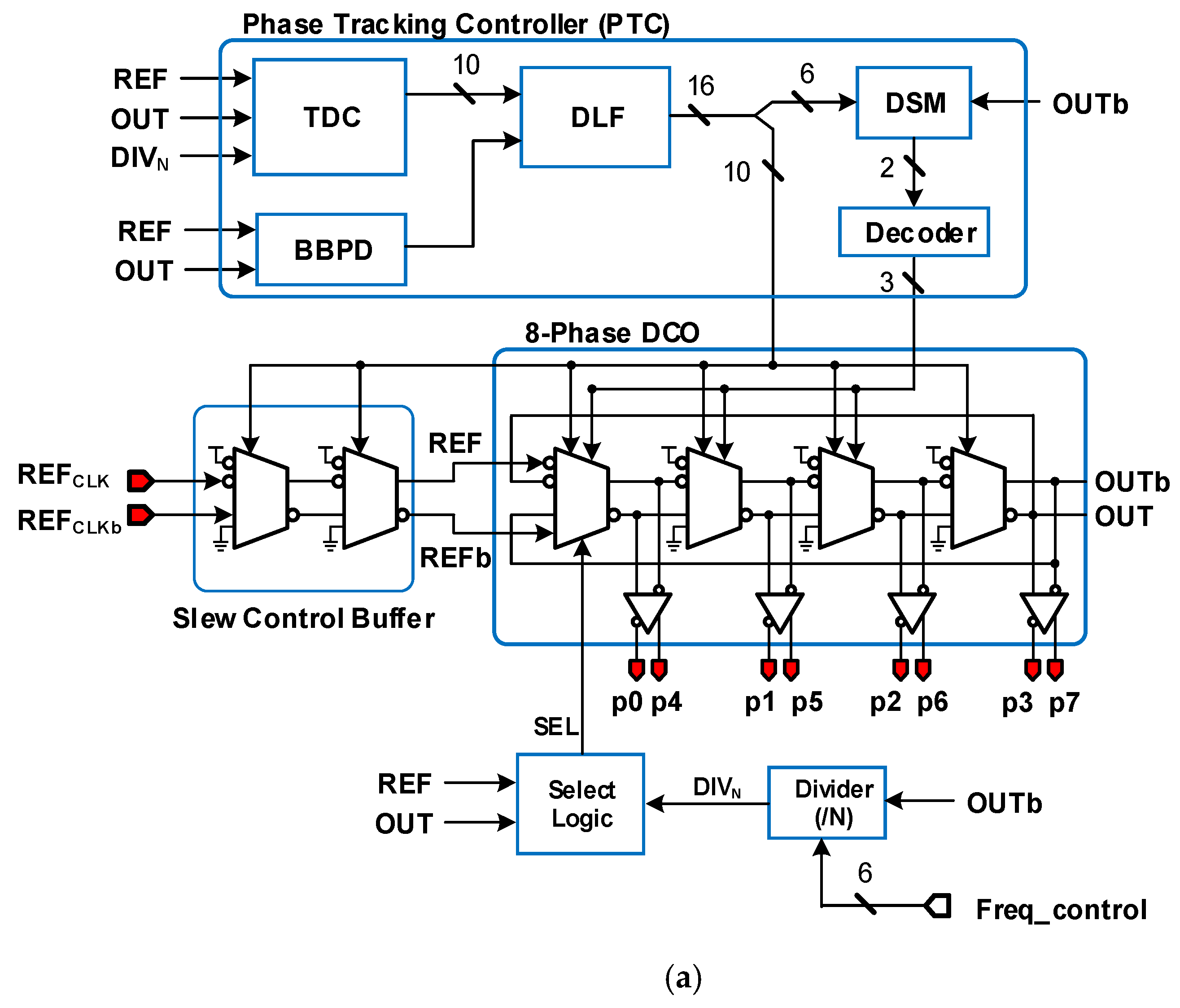

Jitter Amplification Simulation Method Download Scientific Diagram It has the capability for you to apply custom jitter modulation to any wav file, and includes correlated, 1 f, and specific frequencies jitter modulation. because you can apply this to any music track, you can check at what levels jitter becomes audible to you. Explore a methodology for accurate and efficient jitter modeling and simulation in pll frequency synthesizers. learn about phase domain noise, jitter definitions, and behavioral models for verilog a and spectrerf. The undesired variation of the pll operation due to internal and external noise sources are hard to predict and simulate. but it is essential to be able to predict and verify the timing performance of pll in the presence of internally and externally generated jitter and phase noise. This is a small open source python program you can use to bake jitter into an audio file (for testing or educational purposes, fun, or to simply color a piece of music, or whatever else you want of course ).

Jitter Amplification Simulation Method Download Scientific Diagram The undesired variation of the pll operation due to internal and external noise sources are hard to predict and simulate. but it is essential to be able to predict and verify the timing performance of pll in the presence of internally and externally generated jitter and phase noise. This is a small open source python program you can use to bake jitter into an audio file (for testing or educational purposes, fun, or to simply color a piece of music, or whatever else you want of course ). Abstract — a methodology is presented for predicting the jitter performance of a phase locked loop (pll) using simulation that is both accurate and efficient. the methodology begins by characterizing the noise behavior of the blocks that make up the pll using transistor level simulation. Simulations of phase delay, saturation, inter modulation distortion, over sampling, jitter, dither and filter pre ringing. lots of controls and interactive graphs. Convert phase noise into period jitter through integration. visualize offsets, rms timing, and exports. useful for oscillator, clock, and timing design verification workflows. One of the major concerns in the design of plls is noise or jitter performance. jitter from the pll directly acts to degrade the noise floor of an analog receiver and the bit error rate of a digital receiver.

Oscillator Jitter Simulation At Steven Brothers Blog Abstract — a methodology is presented for predicting the jitter performance of a phase locked loop (pll) using simulation that is both accurate and efficient. the methodology begins by characterizing the noise behavior of the blocks that make up the pll using transistor level simulation. Simulations of phase delay, saturation, inter modulation distortion, over sampling, jitter, dither and filter pre ringing. lots of controls and interactive graphs. Convert phase noise into period jitter through integration. visualize offsets, rms timing, and exports. useful for oscillator, clock, and timing design verification workflows. One of the major concerns in the design of plls is noise or jitter performance. jitter from the pll directly acts to degrade the noise floor of an analog receiver and the bit error rate of a digital receiver.

Oscillator Jitter Simulation At Steven Brothers Blog Convert phase noise into period jitter through integration. visualize offsets, rms timing, and exports. useful for oscillator, clock, and timing design verification workflows. One of the major concerns in the design of plls is noise or jitter performance. jitter from the pll directly acts to degrade the noise floor of an analog receiver and the bit error rate of a digital receiver.

Oscillator Jitter Simulation At Steven Brothers Blog

Comments are closed.