Solved Verilog Codingplease Write A Gate Level Verilog Code Chegg

Verilog Gate Level Modeling Pdf 1) write a verilog a) gate level description & b) continuous assignment with the keyword assign of the circuits shown below. provide a simulation using edaplayground by writing a simple test bench for each of them. Some of the main built in primitives were discussed in the previous article and it would be good to see some practical examples of using simple and, nor and not gates. note that in order to write the verilog code using gates, it is necessary for you to know how to connect the elements.

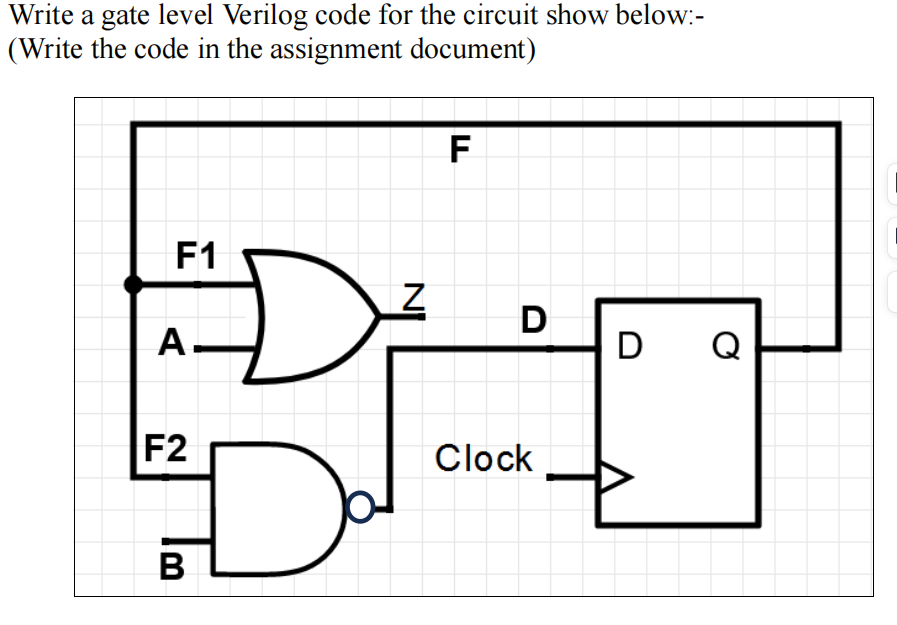

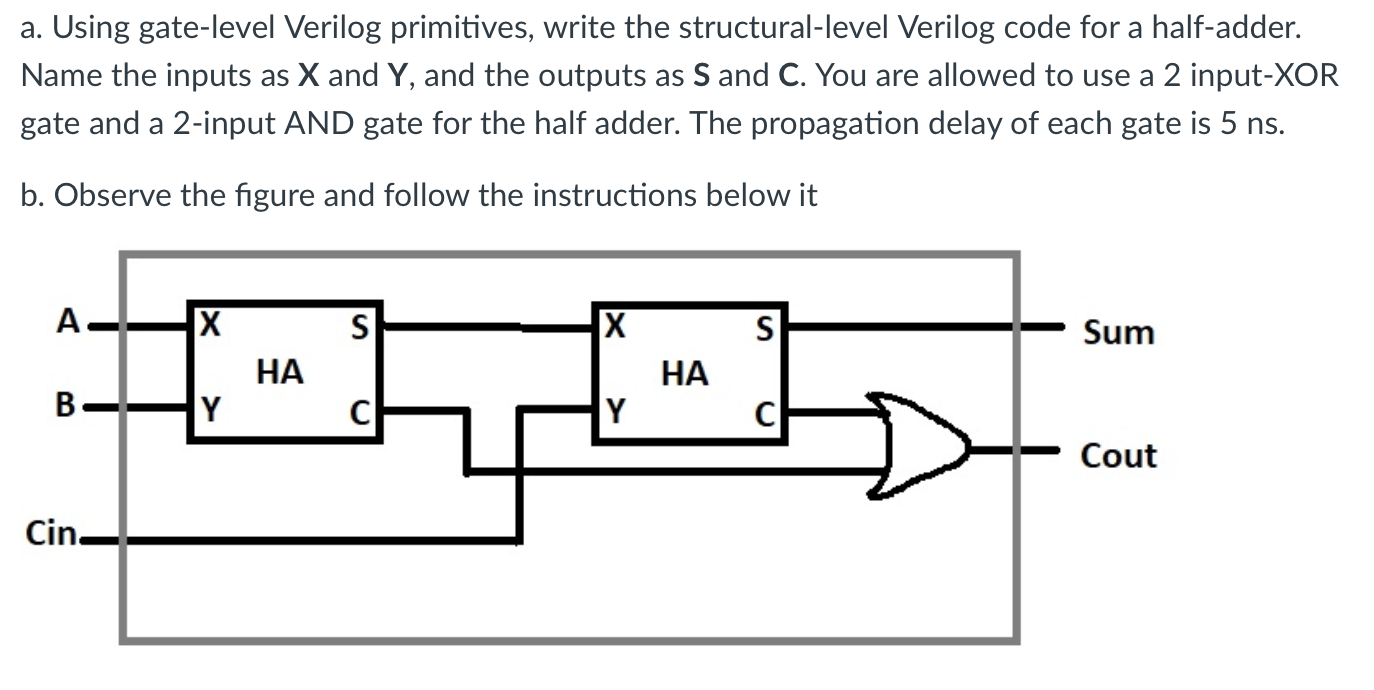

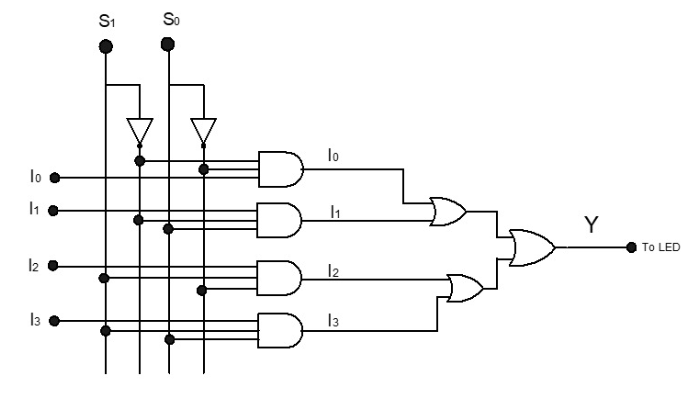

Solved Write A Gate Level Verilog Code For The Circuit Show Chegg This tutorial teaches gate level modeling in verilog with practical examples like a half adder, full adder, and multiplexer using primitive gates. The document contains verilog code for various basic logic gates and their test benches, including nand, not, or, and, xor, and full adder gates. it provides both behavioral and structural descriptions for the gates using primitive gates like nand and not. Learn how gate level modeling works in verilog, how to use primitive gate instantiations, and its applications in low level hardware design and simulation. The three levels of verilog abstraction verilog supports three distinct levels of design description, each mapping to a different phase of the rtl to gdsii flow: gate level modeling is the lowest software expressible abstraction — the direct description of a circuit as an interconnection of logic gates, buffers, and flip flops.

Lab 4 Verilog Gate Level Modelling Pdf Hardware Description Learn how gate level modeling works in verilog, how to use primitive gate instantiations, and its applications in low level hardware design and simulation. The three levels of verilog abstraction verilog supports three distinct levels of design description, each mapping to a different phase of the rtl to gdsii flow: gate level modeling is the lowest software expressible abstraction — the direct description of a circuit as an interconnection of logic gates, buffers, and flip flops. Gate level modeling in verilog explicitly describes circuits as interconnected logic gates. this approach is essential when precise control over hardware implementation is required, such as in timing critical or resource constrained designs. Learn how to write verilog code for an and gate using gate level, dataflow, and behavioral modeling. this guide includes explanations, verilog examples, rtl schematics, and a testbench for simulation. These three examples will help you clear out the idea of gate level modelling using verilog. if you have any confusion or questions please write in a comment section. Implement the circuit described by the following verilog code in cmos using n mos and p mos transistors.

Solved A Using Gate Level Verilog Primitives Write The Chegg Gate level modeling in verilog explicitly describes circuits as interconnected logic gates. this approach is essential when precise control over hardware implementation is required, such as in timing critical or resource constrained designs. Learn how to write verilog code for an and gate using gate level, dataflow, and behavioral modeling. this guide includes explanations, verilog examples, rtl schematics, and a testbench for simulation. These three examples will help you clear out the idea of gate level modelling using verilog. if you have any confusion or questions please write in a comment section. Implement the circuit described by the following verilog code in cmos using n mos and p mos transistors.

Solved Verilog Code Gate Level Code Chegg These three examples will help you clear out the idea of gate level modelling using verilog. if you have any confusion or questions please write in a comment section. Implement the circuit described by the following verilog code in cmos using n mos and p mos transistors.

Solved Verilog Codingplease Write A Gate Level Verilog Code Chegg

Comments are closed.