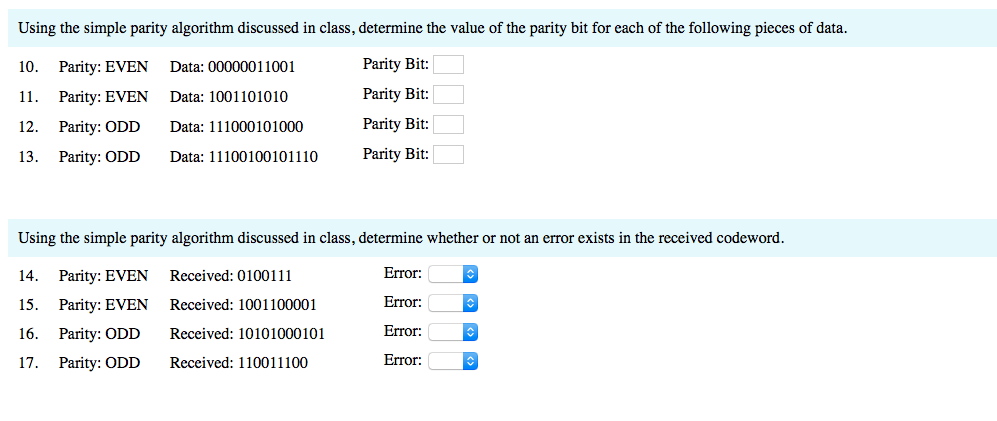

Solved Using The Simple Parity Algorithm Discussed In Class Chegg

Solved Using The Simple Parity Algorithm Discussed In Class Chegg This offer is not valid for existing chegg study or chegg study pack subscribers, has no cash value, is not transferable, and may not be combined with any other offer. Your solution’s ready to go! our expert help has broken down your problem into an easy to learn solution you can count on. see answer.

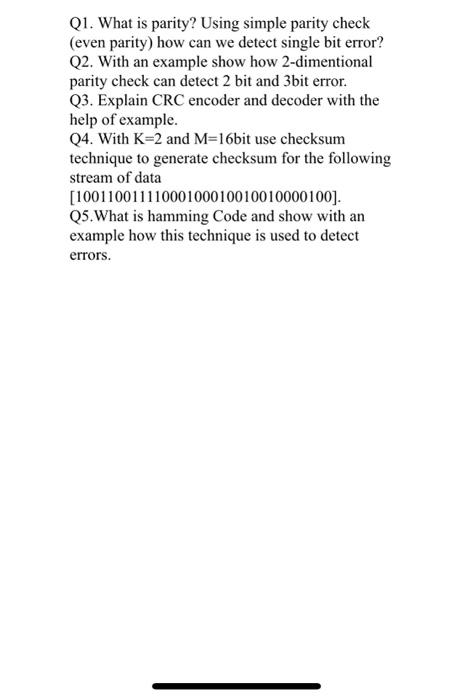

Solved Q1 What Is Parity Using Simple Parity Check Even Chegg Our expert help has broken down your problem into an easy to learn solution you can count on. One of the simplest methods of verification is the parity check. parity is a control code we can use to prevent errors in data reception or reading on mass memories, adding redundant information. When the data is transmitted, the receiver checks the parity bit against the data bits. if the number of 1s in the data bits is even, the parity bit should also be 0. Step 1: write the bit positions starting from 1 in binary form (1, 10, 11, 100, etc). step 2: all the bit positions that are a power of 2 are marked as parity bits (1, 2, 4, 8, etc). step 3: all the other bit positions are marked as data bits.

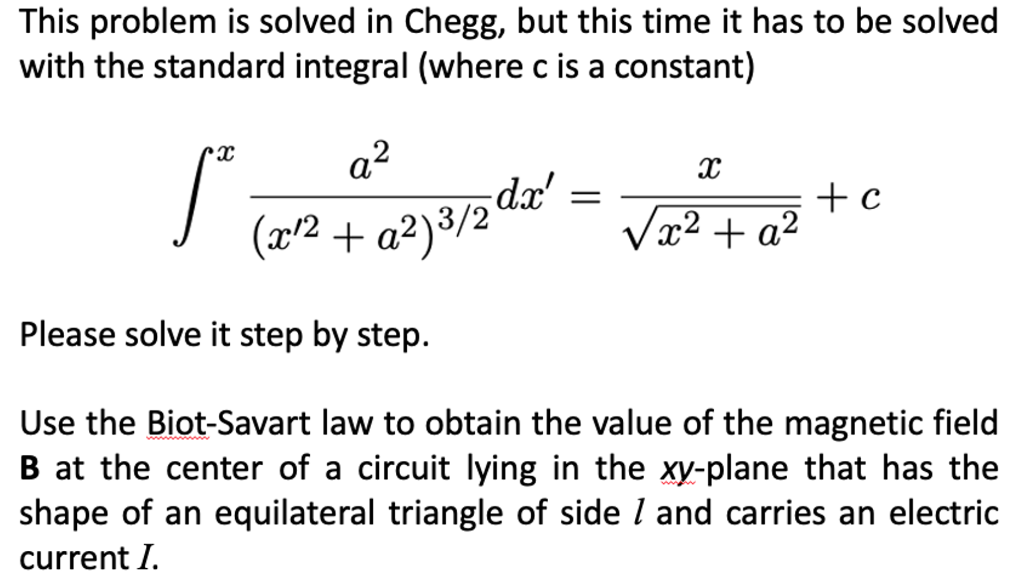

Solved This Problem Is Solved In Chegg But This Time It Has Chegg When the data is transmitted, the receiver checks the parity bit against the data bits. if the number of 1s in the data bits is even, the parity bit should also be 0. Step 1: write the bit positions starting from 1 in binary form (1, 10, 11, 100, etc). step 2: all the bit positions that are a power of 2 are marked as parity bits (1, 2, 4, 8, etc). step 3: all the other bit positions are marked as data bits. Simple party check method is based on parity. so, let me first tell you, how can we compute parity of given data unit?. In structural verilog, we describe a digital circuit as a hierarchy of interconnected modules. each module is defined using its own input, output, and internal signals. we instantiate modules and connect their signals together to create the desired circuit. Error detection in computer networks is a method to detect errors in the data introduced during transmission. single parity check uses a parity bit to perform error detection. cyclic redundancy check (crc) and checksum are other error detection methods. Suppose that a packet’s payload consists of 10 eight bit values (e.g., representing ten ascii encoded characters) shown below. (here, we have arranged the ten eight bit values as five sixteen bit values): both the payload and parity bits are shown. one of these bits is flipped.

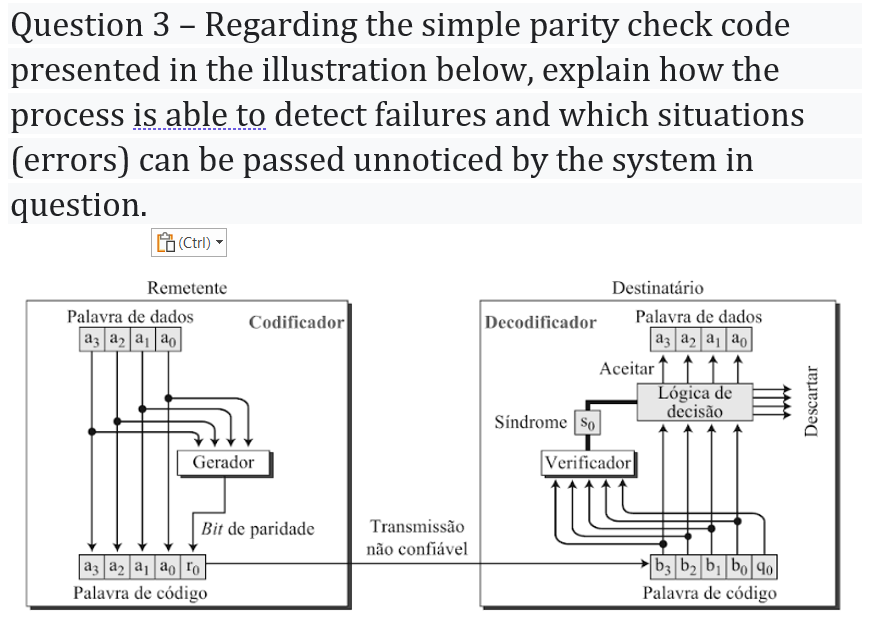

Solved Question 3 Regarding The Simple Parity Check Code Chegg Simple party check method is based on parity. so, let me first tell you, how can we compute parity of given data unit?. In structural verilog, we describe a digital circuit as a hierarchy of interconnected modules. each module is defined using its own input, output, and internal signals. we instantiate modules and connect their signals together to create the desired circuit. Error detection in computer networks is a method to detect errors in the data introduced during transmission. single parity check uses a parity bit to perform error detection. cyclic redundancy check (crc) and checksum are other error detection methods. Suppose that a packet’s payload consists of 10 eight bit values (e.g., representing ten ascii encoded characters) shown below. (here, we have arranged the ten eight bit values as five sixteen bit values): both the payload and parity bits are shown. one of these bits is flipped.

Comments are closed.