Solved Question 3 Verilog Using Structural Gates A Chegg

Solved Question 3 Verilog Using Structural Gates A Chegg Write the verilog code for 3 input and gate using structural modeling using two 2 input and gates. there are 3 steps to solve this one. the given problem requires simplifying boolean not the question you’re looking for? post any question and get expert help quickly. To create a 3 input and gate using structural modeling in verilog, you can utilize two 2 input and gates. below is the verilog code for this implementation:.

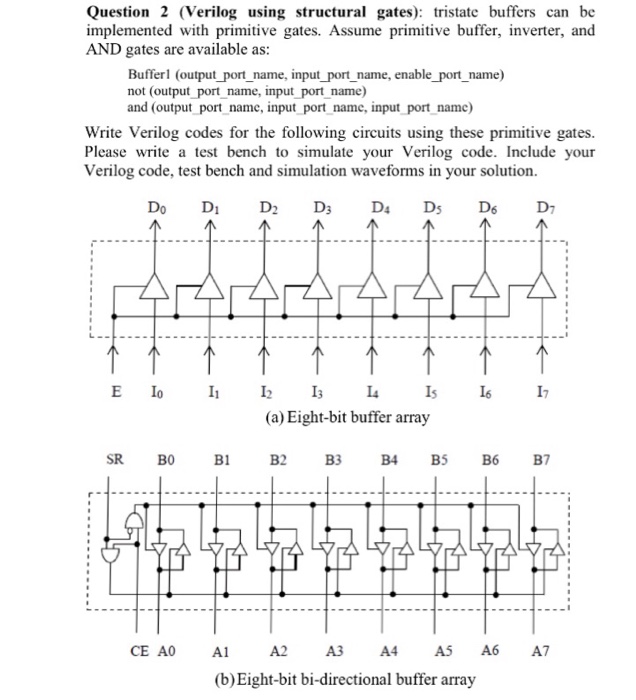

Solved Question 3 Verilog Using Structural Gates A Chegg Problem 6: create a structural verilog model for a simple bit alu that sup ports addition, subtraction, multiplication, logical and, logical or, and logical xor. This chapter discusses structural modeling in verilog using primitive gates and switches. it covers primitive gates like and, or, not etc. and how they can be instantiated and connected. Question (verilog using structural gates): tristate buffers can be implemented with primitive gates. assume primitive buffer, inverter, and and gates are available as: buffer1 (output port name, input port name, enable port name), inverter (output port name, input port name), and and (output port name, input port name, input port name). Learn structural design with verilog. covers modeling, operators, flip flops, state machines, and style guidelines. ideal for college level electrical engineering.

Solved Question 2 Verilog Using Structural Gates Tristate Chegg Question (verilog using structural gates): tristate buffers can be implemented with primitive gates. assume primitive buffer, inverter, and and gates are available as: buffer1 (output port name, input port name, enable port name), inverter (output port name, input port name), and and (output port name, input port name, input port name). Learn structural design with verilog. covers modeling, operators, flip flops, state machines, and style guidelines. ideal for college level electrical engineering. You can define the structural model of a hardware module using four techniques: gate instantiation, switch instantiation, udp instantiation, and module instantiation. In gate level modelling, we use primitive gates to model a circuit depending on its schematic diagram. this is part – 1 of tutorial on structural modelling. these gates can have ‘n’ inputs, and one output. the truth tables of the above gates are given below. Verilog is a powerful language and offers several different levels of descriptions. the lowest level is the gate level, in which statements are used to define individual gates. in the structural level, more abstract assign statements and always blocks are used. After switch level modeling, structural modeling is the lowest level of abstraction in verilog. it is also called gate level modeling because we only describe a hardware in logic gates and their inteconnections.

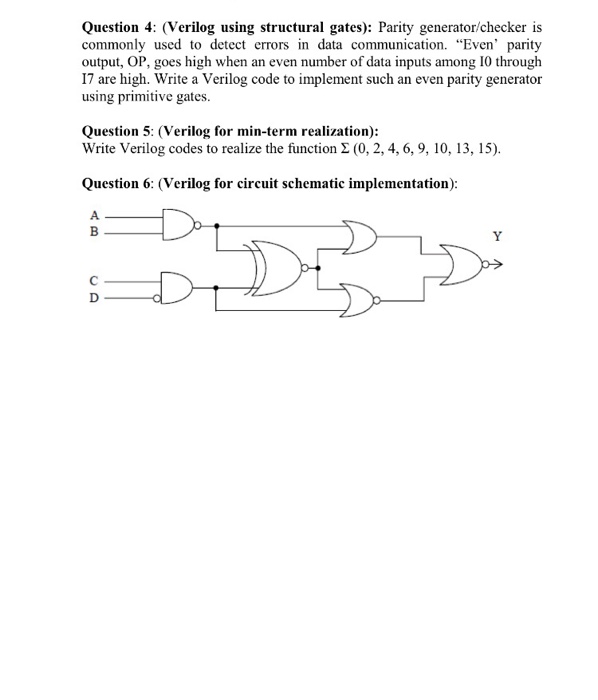

Solved Question 4 Verilog Using Structural Gates Parity Chegg You can define the structural model of a hardware module using four techniques: gate instantiation, switch instantiation, udp instantiation, and module instantiation. In gate level modelling, we use primitive gates to model a circuit depending on its schematic diagram. this is part – 1 of tutorial on structural modelling. these gates can have ‘n’ inputs, and one output. the truth tables of the above gates are given below. Verilog is a powerful language and offers several different levels of descriptions. the lowest level is the gate level, in which statements are used to define individual gates. in the structural level, more abstract assign statements and always blocks are used. After switch level modeling, structural modeling is the lowest level of abstraction in verilog. it is also called gate level modeling because we only describe a hardware in logic gates and their inteconnections.

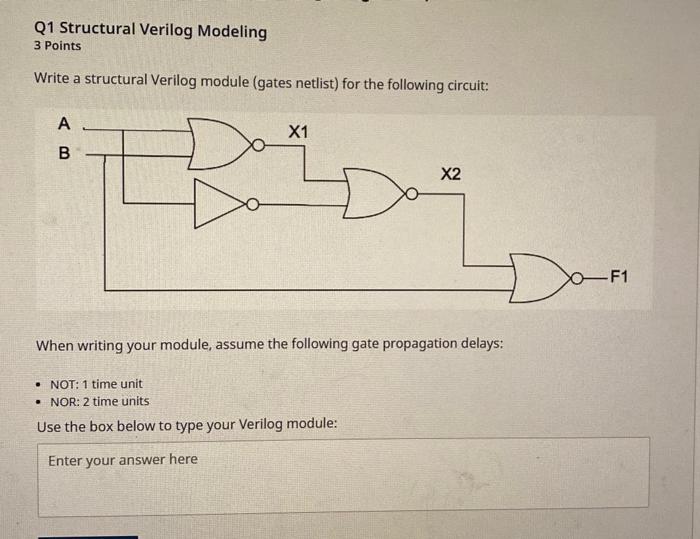

Solved Q1 Structural Verilog Modeling 3 Points Write A Chegg Verilog is a powerful language and offers several different levels of descriptions. the lowest level is the gate level, in which statements are used to define individual gates. in the structural level, more abstract assign statements and always blocks are used. After switch level modeling, structural modeling is the lowest level of abstraction in verilog. it is also called gate level modeling because we only describe a hardware in logic gates and their inteconnections.

Comments are closed.